Quartus本身有提供內部LA的debug工具Singal Tap,不過該工具在合成的時候是會占用FPGA內部空間的,所以你要看的PIN越多,或者設定的記憶體深度越深,占用的空間就會越多。

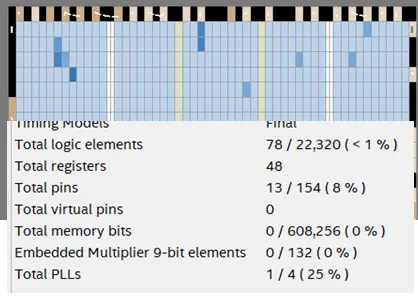

沒有Singal Tap的合成占用的空間:本身的範例很簡單,其實只佔用幾個邏輯閘而已。

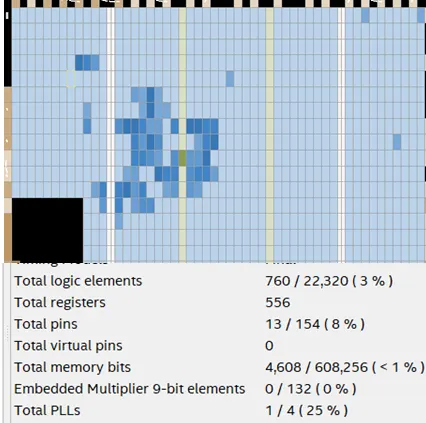

有

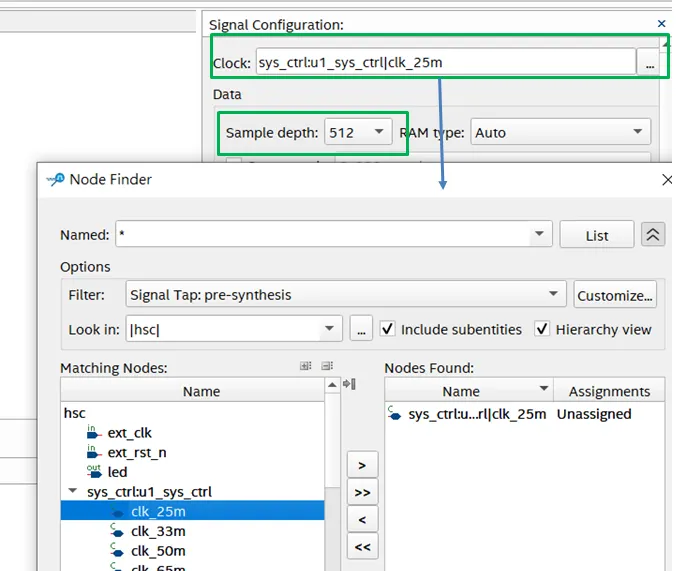

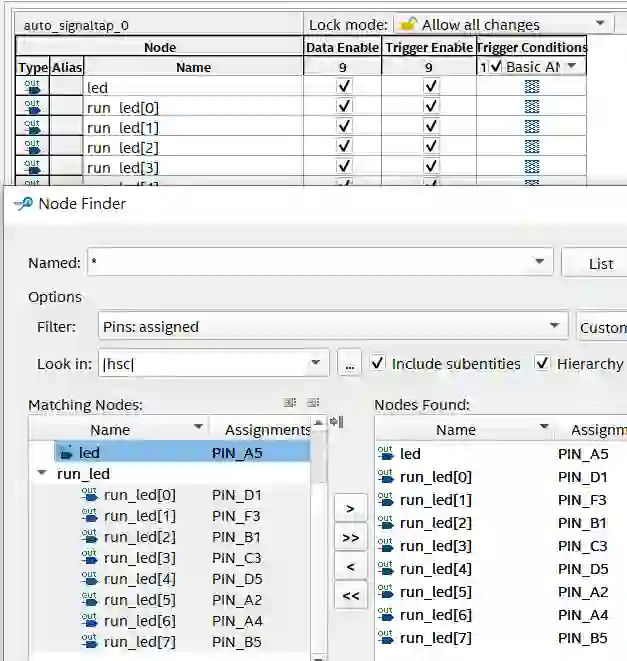

Singal Tap的合成占用的空間:這邊的範例只是拉出8根PIN來觀察,記憶體深度512

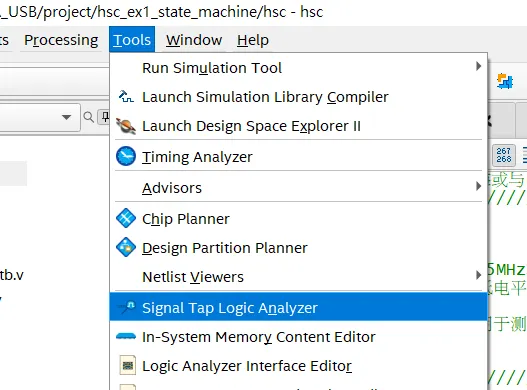

設定順序:

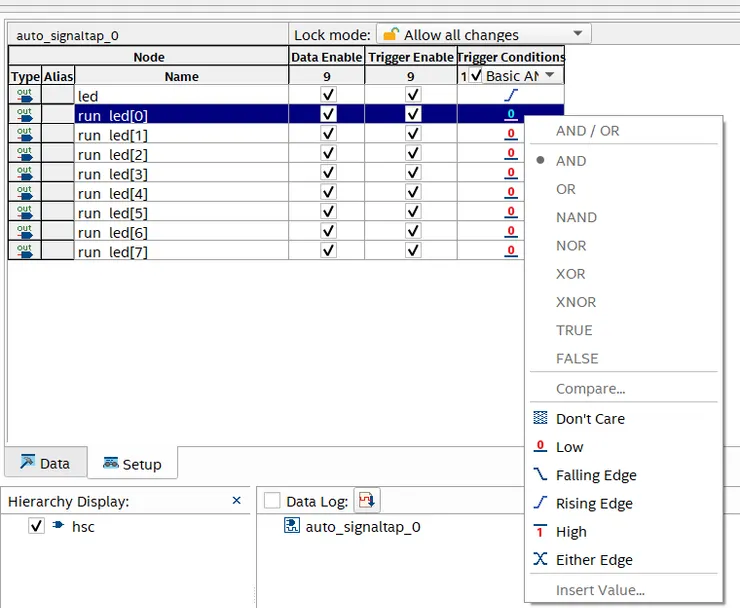

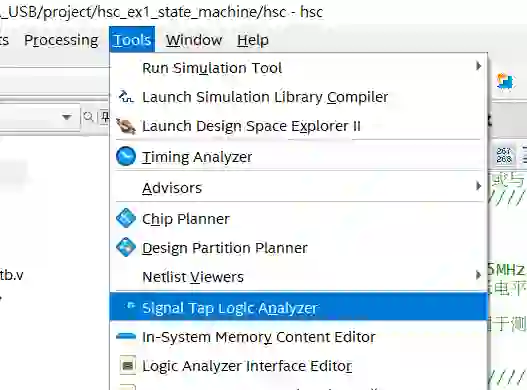

- Tools -->Signal Tap Logic Analyzer開啟編輯

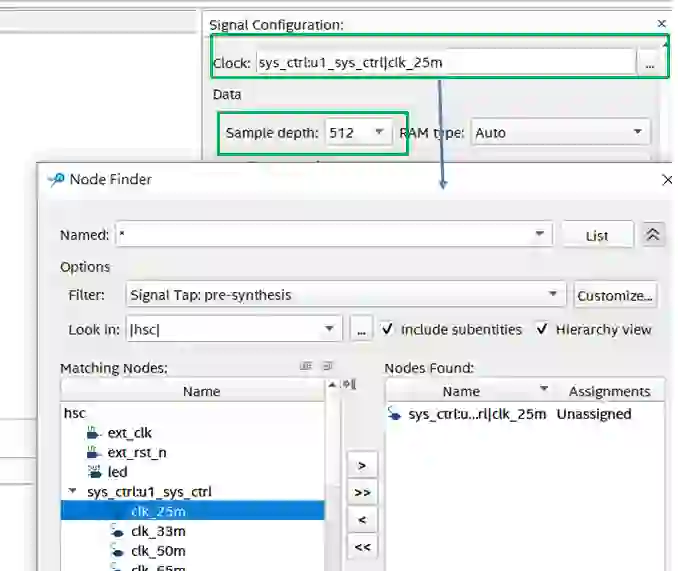

- 右邊選項先設定我們的LA的clock與取樣的深度。

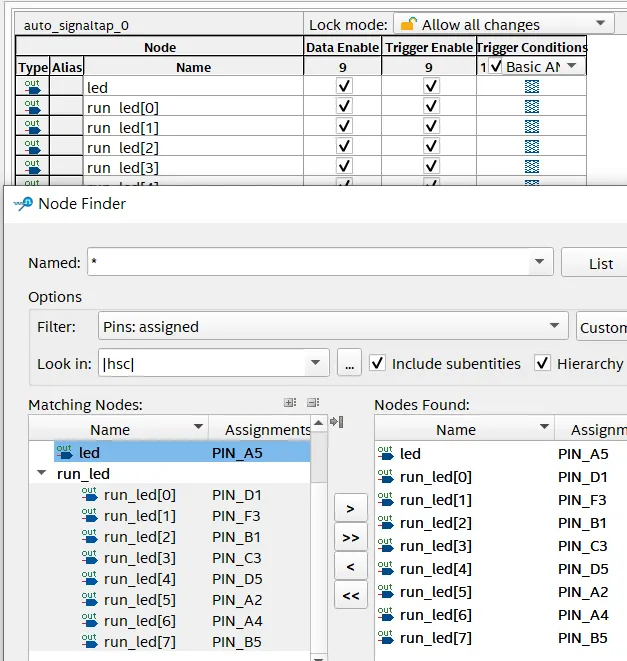

- 左邊空白處滑鼠左鍵點兩下,加入我們要觀察的PIN

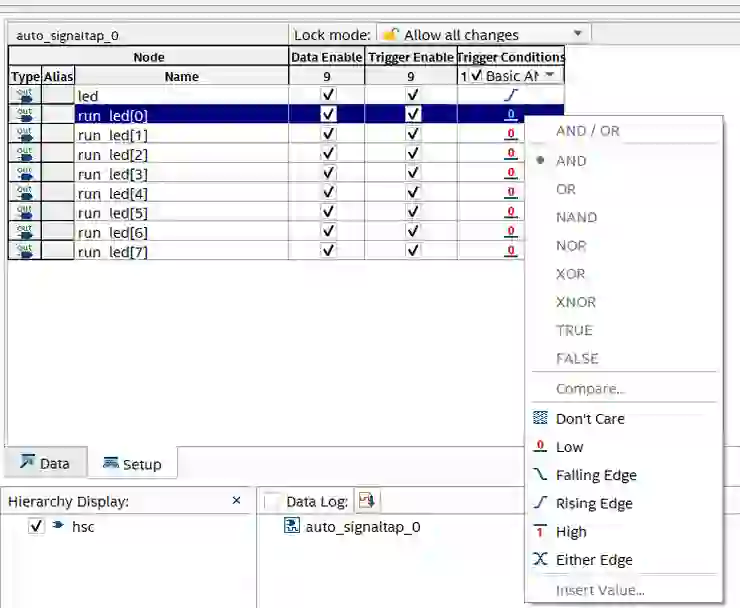

- Trigger conditions這邊設定我們要觸發的條件,其實開始debug的時候也可以用,這邊先做好會有一個預設設定的效果。

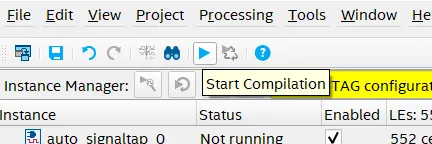

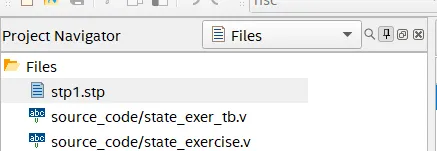

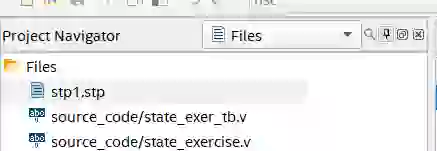

- 重新存檔並compiler,這時候會發現Project Navigator這邊多了一個我們的stp file

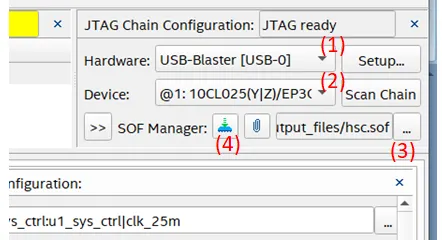

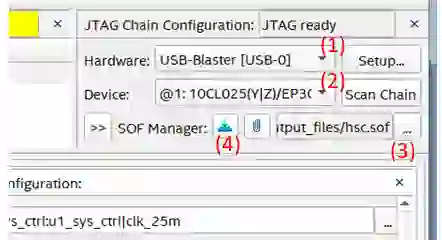

- 回到signal tap畫面,設定我們的燒錄器並偵測device後,加入我們compiler後的sof file,最後按下燒錄

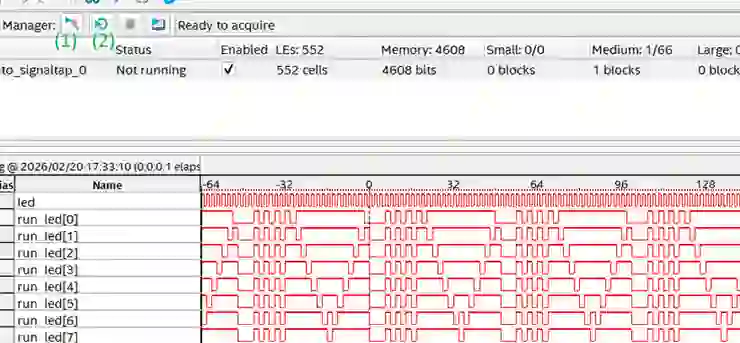

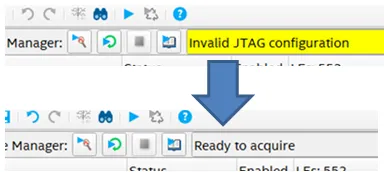

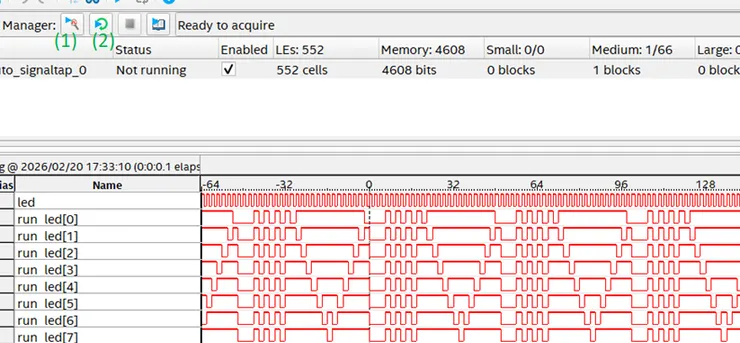

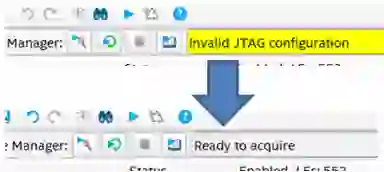

- 出現Read to acquire就是燒錄成功了

- 執行(1)或(2)就可看到我們設定的觸發訊號,這兩個的差別在於一個只觸發一次,一個只要滿足條件就會一直抓訊號進來更新。