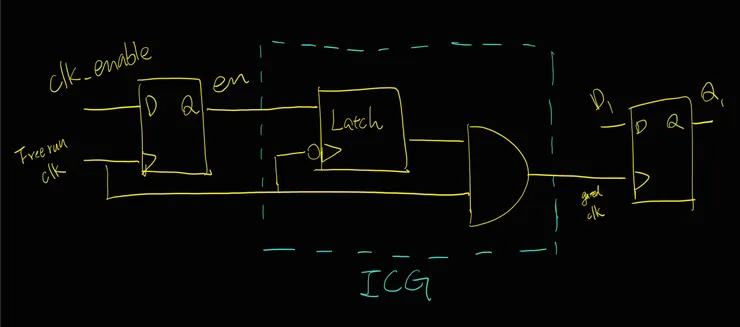

前面文章提到過clk gating check實際上就是在check gating cell的enable訊號

檢查enable的timing是否能滿足STA的check,

不過不知道各位有沒有發現到,

這條path看起來很單純呀而且我還用上了latch大法,

可能讓訊號走完1整個cycle,為甚麼有時候還是會看到setup time violation?

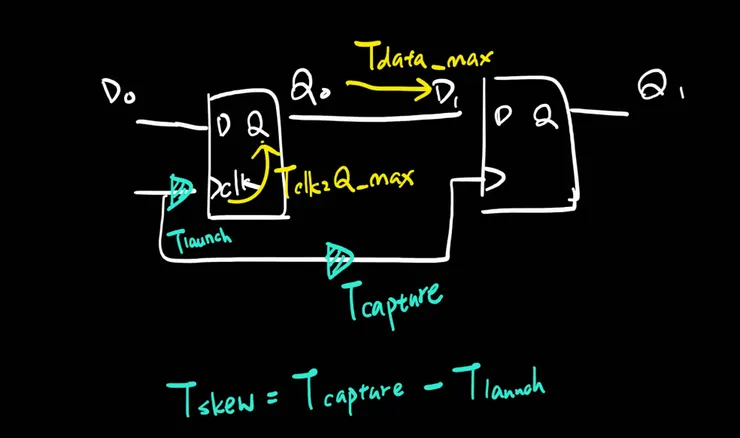

在這邊我們先複習一下setup time violation是如何檢查的

[Verilog] STA分析 - setup / hold violation 怎麼workaround

[Verilog] clk skew vs clk jitter

文章內提到

Tcycle + Tskew >= Tclk2Q_max + Tdata_max +Tsetup

其中的Tskew指的就是clk從source出發後

因為reg0和reg1的placement位置不同導致抵達的reg clk pin上的時間會有落差

因此可以在拆解的細一點

對於另外一種描述setup check的方式分為 data arrival time 和 date required time

arrival <= required 則meet setup time

arrival time = Tlaunch + Tclk2Q_max + Tdata_max

required time = Tcapture + Tcycle - Tsetup

arrival <= require :

Tlaunch + Tclk2Q_max + Tdata_max < Tcapture + Tcycle - Tsetup

轉換一下 -> Tcycle + (Tcapture - Tlaunch) > Tclk2Q_max + Tdata_max + Tsetup

又 Tskew = Tcapture - Tlaunch 因此最後可以推回上面原先的公式

Tcycle + Tskew >= Tclk2Q_max + Tdata_max +Tsetup

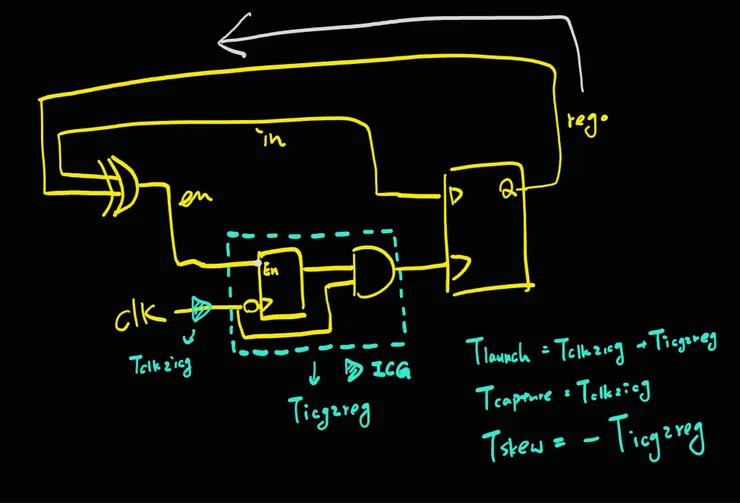

好啦,那回到原先的問題,為甚麼我的clk gating path看起來很簡單卻還是會碰到Setup time violation,

因為其實上面的圖中是有一些盲點的,

我們直覺地都會認為clk->reg0 的速度一定會快於clk->reg1的速度,

因此skew扣出來都是正的,正的skew下有利於setup time的收斂,

不過因為實際上我們clk gating 的enable訊號組成大部分時候都是靠某些reg的output的結果重新組出來的條件,

所以這種情況下,在CG身上看到的skew是負的

舉個例子

always @ (posedge clk_gated or negedge rst) begin

if (!rst)

reg0 <= 1'b0;

else

reg0 <= in;

end

assign clk_gated = clk & clk_en ;

assign clk_en = (reg0 != in) ;

對於上面的code來說,

假設一下clk & clk_en會產出icg,

reg0的clk_gated是當clk_en ==1的時候才會toggle的,

clk_en 為1的條件則為reg0的output 不等於輸入in,

因此在這個情況下電路大致會長成以下樣貌

timing check point會在latch的enable上

Tcycle + (Tcapture - Tlaunch) > Tclk2Q_max + Tdata_max + Tsetup

Tcycle 不變為1T

Tcapture = Tclk2icg

Tlaunch = Tclk2icg + Ticg2reg

Tclk2Q_max = latch內鎖住en的耗時被包含在Ticg2reg內

Tdata_max = 後級reg0所打出來的Q output

也就是說這級的timing check不是像先前一樣一級推一級,

而是拉了一個迴授的感覺,由後級往前級推,也因為這個迴授

讓skew變為負值,原本能靠skew偷到多一點的setup margin直接消失,

並且Tdata_max會隨著en組成的複雜度增長,

也因此有時候我們會發現好像clk path上很單純,

但是卻出現了timing violation

想必各位在碰到這邊跳出violation時也十分困擾,

因為他不像一般寫code一樣setup time violation那就多切幾級pipeline就好了,

有時候根本不知道該如何下手,

這邊就提供幾個經驗,

通常最簡單的方式就是研究一下en訊號是否組成太複雜,

clk gating 使用的效率實際上有一些指標可以看,

最簡單的判斷方式就是同一顆gating cell control了多少的reg量,

因為gating cell本身也是會耗power和area因此沒辦法無腦塞,

所以會希望說一顆cell能gating越多reg越好,

不過同時可能就會讓enable的條件變得複雜,

並且從icg出來到各個reg/ck的wire delay十分長,

也間接地拉高了Tdata_max和Ticg2reg,

因此就這個現象最直接的解法就是,

縮小gating cell的fanout,

用以降低en的複雜度同時可以讓cell擺的離reg近一點縮短wire delay

但是有時候看到violation的時機總是有點尷尬在apr才看到,

總是感覺很奇怪,

我明明在synthesis的時候timing都clean了沒有看到任何violation,

apr的時候BE卻跟我說clk gating cell上跳setup violation我該怎辦,

到底是哪個Tool錯了?

冷靜思考一下發現

原來是因為我們在synthesis的時候cell placement的位置都是未知的呀,

clk端也不會長clk tree,

因為這些部分都在apr的階段才會做處理,

所以這時候看到violation也只能硬著頭皮解,

當然最簡單的解法就是看一下是否能把cg cell往timing violation的reg靠近一點,

降低wire delay (降低skew),

不過很有可能牽一髮動全身,換別條path跳出來

所以再好幾天沒睡東瞧瞧西瞧瞧後還是走投無路的情況下

在這邊提供最強的大絕招給各位

讓各位可以從地獄解脫

ECO把clk_en 直接 tie 1 !!!

不要讓clk gating生效了,

也就是說當作沒有這顆clk gating,

當然這樣做也會帶來一些impact,

不過這個impact是屬於power bug不是function bug,

對於function使用上完全沒問題,還可以讓你從地獄解脫,完美

#clock gating check #CG #STA #low power #clock gating check #setup time #hold time #ECO