前面文章曾經提到說,

除了我們在寫rtl當下直接撰寫加入的cg cell外,

實際上我們有些clk gating cell是靠tool自己幫忙插的,

[Verilog] 10分鐘由淺入深看懂 clock gating -2

那麼tool是怎麼判斷說哪邊要插gating cell的呢?

這個自動產生clk gating cell的stage位於synthesis階段,

透過enable insert_clock_gating及給予相關設定後來生效function,

所以有時候會發現說,怎麼netlist的內容物和rtl level有些差異,

就是因為在某些coding style下會誘發synthesis tool幫忙做cg的insert,

以提供netlist有更好的power consumption.

我們在撰寫verilog時,經常都會使用到某些condition來作為enable的訊號,

對於always block內如果結束在else if而不是else的話,

tool就會幫忙對這個reg做CG的insertion,

然而相關的condition也會被融入到cg en的條件內.

else if版本 tool將幫忙產生cg

always @ (posedge clk or negedge rst) begin

if (!rst)

reg0 <= 5'b0;

else if (condiction)

reg0 <= input;

end

else版本 不會產生cg

always @ (posedge clk or negedge rst) begin

if (!rst)

reg0 <= 5'b0;

else

reg0 <= input;

end

然而對於cg cell來說,

也是會有一定的area和power的低消,

所以tool中有minimum bits的設定可以使用,

當reg 的bits數小於min bits時則不會做相關的insertion,

才不會因為CG cell的關係導致power consumption比原本來得更大.

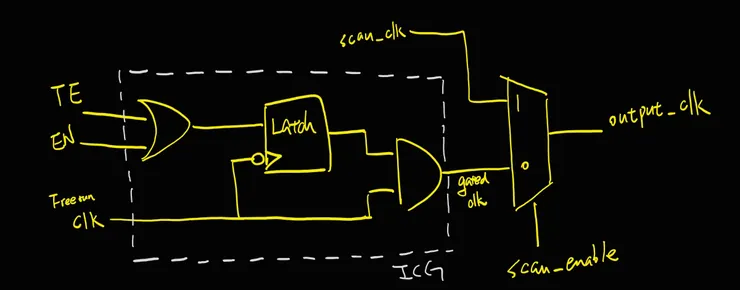

此外,大家在實際的netlist中可能會發現,

CG cell除了上述描述到的port之外,

還多了一隻叫TE的port,

以下圖為例

TE port 為test enable的輸入,

當ic 切到test mode下時,必須要保證clk不會被normal function切掉,

盡可能使register都是在可觀且可控的條件下做scan test,

因此對於cg的module通常都會開出一隻TE腳位讓user去接上scan_enable或test_mode的訊號,

TE或EN兩者其中一個為1時就會釋放clk給下游的register,

使cg cell接到的reg不會因為normal function的關係導致在scan test時沒有clk使用,

藉由多開出一條TE port來提高dft的coverage,

然而TE port所接的訊號要使用test_mode或是scan_enable亦或是新的control reg出來得訊號則因各個design來定.