D型正反器的輸出,直接由外界輸入來決定,如同一個專門儲存從D輸入端進來資料的記憶裝置,故D型正反器即資料型正反器,由於其構造簡單且容易儲存暫時性資料,廣泛用於資料暫存器、移位暫存器、計數器等。

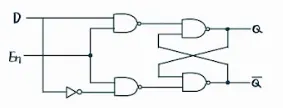

D型正反器內部結構和RS正反器相像,只不過輸入其中一端多了一個NOT閘:

在上圖,只要將En改為邊緣觸發檢測器即為D正反器了。

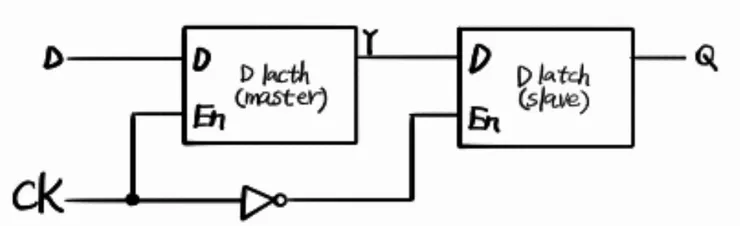

另外,我們同樣可以使用 兩個 D 閂鎖器與一個反相器(inverter)來構成D正反器。

稱為主從式 D 正反器(Master-Slave D flip-flops)。

說明如下:

- 當CK為1時,主閂鎖器致能訊號為1(致能),僕人閂鎖器致能訊號為0(禁能)

- 如果此時此時輸入訊號是 D(t),由於主閂鎖器是打開來的,所以會更新資料反映到輸出端 Y,也就是 Y = D(t)。

- 而此時僕人閂鎖器是禁能的狀況,Y = D(t)並不會被傳入,輸出還是維持在之前的狀態,所以是不變的情形。

- 現在考慮CK為0時,主閂鎖器致能訊號為0(禁能),僕人閂鎖器致能訊號為1(致能)

- 那麼假設在此時輸入訊號變為D(t+1),但是因為主閂鎖器是鎖上的情形,Y 並不會被改變,還是維持在之前的結果 Y = D(t)。

- 而僕人閂鎖器是致能的情形,就會把 Y = D(t) 傳送到輸出端 Q 來,這個動作就好像是在CK由1變為0時,將 D(t) 做寫入 Q 的一個行為。

- 所以此主僕式為一個負緣觸發 D 正反器。

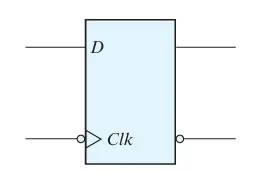

D正反器其符號如下圖所示(負緣觸發):

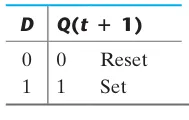

其功能表如下所示:

可以輕易看出,D正反器觸發後的輸出端會等於輸入端的資料。

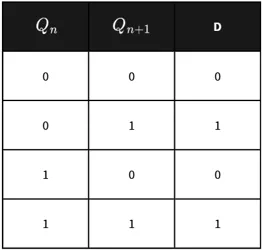

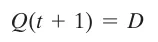

再來,我們繼續探討 D正反器的激勵表與輸出特徵方程式:

- 激勵表

- 輸出特徵方程式

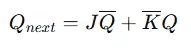

好,由於D正反器的輸出特徵方程式非常簡單直觀,此時你不妨想想,如果我們想要由D型正反器轉換成其他類型的正反器,我們可以透過改變 D 的輸入邏輯為其他正反器的特徵方程式,讓 D flip-flop 模擬出其他類型的正反器(像是 T、JK、SR 等)。我們來看看例子:

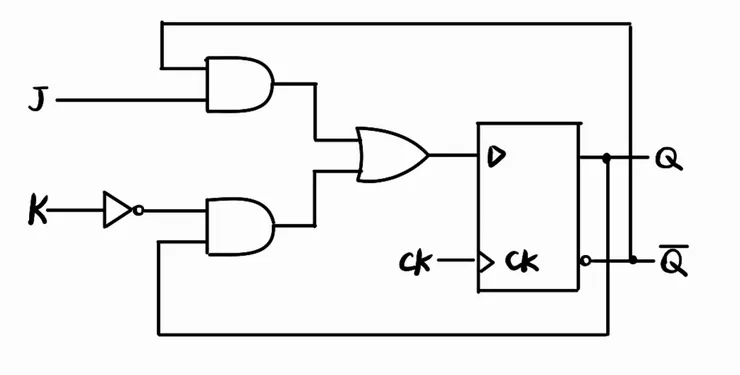

JK flip-flop 的特徵方程式是:

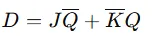

要讓 D flip-flop 模擬它,只需設計:

這樣 D flip-flop 的輸出就會依照 JK flip-flop 的行為改變。

示意圖如下所示:

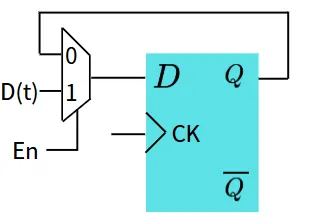

最後的最後,不知道你有沒有這樣想過,像是JK正反器在輸入端同時為0時,輸出端Q會保持不變的狀況,可是D正反器被沒有保持不變的狀況,所以,我們其實可以透過添加一個多工器來實現D正反器保持不變的狀況,如下所示:

- 若

En = 1→ 正常更新。 - 若

En = 0→ 保持原本的狀態