【前言:晶片之後,系統之前】

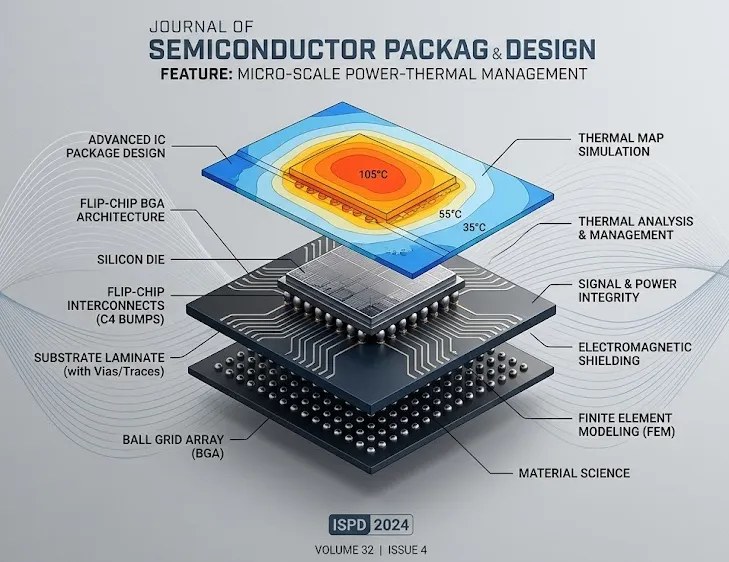

在半導體產業中,當台積電完成了精密的晶片製造後,這顆昂貴的矽晶圓(Die)還不能直接使用。它脆弱、細小,且無法直接與主機板溝通。這就是「封裝設計工程師」登場的時刻。我們的工作,就是在微米($\mu m$)等級的空間裡,為晶片打造最強悍的「盔甲」與「高速公路」。【核心挑戰一:散熱與電磁的永恆戰爭】

封裝設計最迷人也最痛苦的地方在於「權衡(Trade-off)」。當晶片效能越高,產生的熱能就越驚人。

作為設計者,我們在 Simcenter Flotherm 或 Icepak 中模擬熱流,試圖增加散熱片(Heat Sink)或優化導熱膠(TIM);但與此同時,為了追求極致的訊號傳輸速度,我們必須在 Ansys Q3D 或 HFSS 中斤斤計較每一條線路的寄生電感與電容。

- 熱能說:「我需要更多空間散熱。」

- 電性說:「線路要越短越好,阻抗要匹配。」封裝工程師的價值,就在於如何在這一正一反的物理限制中,找到那個「黃金平衡點」。

【核心挑戰二:從 PLMD 到實際落地的距離】

在軟體模擬中,一切都是完美的幾何與邊界條件。然而,實際進入封裝廠(OSAT)打樣時,翹曲(Warpage)、材料熱膨脹係數(CTE)不匹配導致的錫裂,才是真正的夢魘。

我常說,一個好的封裝工程師不能只會畫 CAD 或跑模擬,更要理解材料學與製程能力。當我們在設定 Package Level Model Description (PLMD) 時,背後代表的是對供應鏈與量產良率的深刻理解。

【核心觀點:封裝不再只是配角】

隨著摩爾定律放緩,**「先進封裝(Advanced Packaging)」**與 Chiplet(小晶片) 技術正式走上舞台中央。封裝不再只是晶片的附屬品,而是提升系統效能的關鍵指標。這意味著我們的影響力正從後段製程,回溯到前段的架構設計。

【結語:這是一場微觀的建築工程】

如果你問我這份工作是什麼感覺?我會說,我們是在幾公釐見方的空間裡,蓋一座具備電力、排水(散熱)與抗震(力學)功能的摩天大樓。雖然這份工作充滿了模擬報錯與頻寬壓力,但當你設計的封裝體成功驅動了最新一代的 AI 伺服器時,那種成就感是無可取代的。