以下內容出自本人自身經驗。由於本人只算是在三線(還是三線以下?😅)的晶圓廠工作,並非很先進的廠,根據不同公司、組織、文化...等都會是工作上差異的變因,不過某些部分我相信是科技業、甚至擴及製造業都可以通用的,希望對大家會有幫助 🙌。

又準備到畢業季了 🎓,前陣子各大廠家的校園職涯博覽會也到了一個段落。想當年我對於工廠的職位其實很侷限,只有想到製程、設備、整合工程師,也就是網路上戲稱的「產線三寶」🤣。在學歷跟科系侷限上,身邊的學長姐其實也大多在這些職位上遊走,頂多有些人半路出家成廠務 XD。總之這一篇是希望讓有意擔任製程類的開發/整合工程師的人,對於這個職位有一定的了解。

一、如何應徵上製程類的開發/整合工程師? 💼

在台灣的環境,如果是新鮮人,剛開始的籌碼其實就只有「學歷」,就是如此的簡單暴力 🥊。而學歷科系也會對應到收到的公司層級大小,或是單位的技術難度有所不同。

- 科系與職位的關聯:如果你是所謂的產線系學生,現今台灣的體制下,我個人認為若碩論與半導體有關聯,會比較有機會到整合開發類的職位;若碩論較偏向傳產或是單一製程的,可能就還是純製程的機會較多 🔬。

- 經歷累積:若您自認為學歷科系要一次性應徵到大公司會較為困難,只能先向下求取工作經歷 📉。我自身工作第一年是製程+設備工程師,現職才在三線廠當製程開發工程師一職。

- 招募考科:招募時,製程跟開發工程師肯定少不了考邏輯、細心度、英文這三科 📝。其中我個人認為「邏輯」是最重要的一個,主管在面試前必定會參考該項分數決定是否要面試,或是安排面試順序。而英文可能會根據部門業務性質、主管喜好來決定是否重要。我自己所在的部門是對接到外國客戶 🌎,因此很多案件相關文件都是用英文去書寫,所以基本的聽讀能力需要有。

- 面試重點:面試時面試官會根據你的談話來推測你的人格特質,這邊就是最主觀的部分了 🗣️。每個主管的喜好會不同,大原則就是你整個人的動機邏輯需要明確,有自我學習精進的能力(最好要有例子 💡),待人接物有禮...等。

二、製程開發/整合工程師的工作內容? 🛠️

其實所謂的一線、二線的廠,很多的工作是切的極度細的,照理來說這兩個職位不該合在一起寫。不過因為我在小廠嘛,這邊就加減當參考吧~ 😉

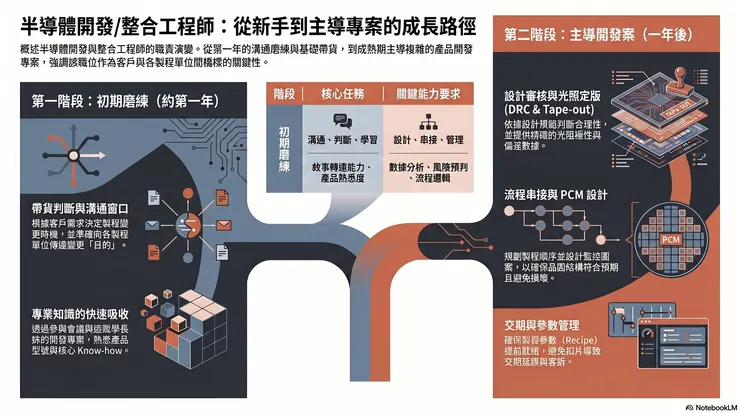

🌱 初期(約第一年):

- 擔任傳遞消息的窗口:熟悉較成熟的產品製程,基本上就是帶一些尚未量產的貨(整合的話就是帶穩定的量產貨)。會根據客戶自身想要做的條件變化,會需要你判斷拆併批站點,以及切出做不同製程條件變更的時機 ⏱️。此時也需要你去通知各大製程單位,你手上的產品需要做的變更條件等等。會根據你收到的條件難易度不同,也會考驗到一個人的敘事轉達能力,此時除了文字繪圖的考驗,最重要的是要「告知目的」 🎯。

- 吸收 Know-how:此階段也要盡量吸收學長姐在做的專案或是較複雜的產品型號。開發案一開始看不懂,我覺得可以先從會議、信件等等較常出現的產品型號來開始做學習 📖;或是同事產品出現 Issue,也是補充你製程 Know-how 的時機,不要認為你以後不會遇到類似的問題。

🚀 脫離新人期(大約一年後?): 若第一年沒有出現什麼問題,主管應該會嘗試給予開發案或是較難的產品要你主導。我個人覺得跟純製程跟設備工程師比起來,整合、開發工程師是職涯上能比較快就能嘗試累積專案的職位(因為另外兩個在前期應該還是以能夠值班為主 🏃♂️)。以下我以開發新產品為例:

- DRC(Design rule)判斷:從一開始客戶寄 Layout 設計進來,你就要根據 DRC 去判斷客戶的設計是否合理,何處需要修正 📐。有些廠系統面較佳可能不需要人工確認,可以先跑程式比對;不過比對出來 fail 的部分當然還是需要人工提出與客戶討論。有時候評估違反的部分可以嘗試做,還是會通過該設計;若確定不行就是會請客戶改設計。DRC 也會根據你搭配的光阻、機台...等不同而有不同,所以跟客戶不只是看設計的大小,更要確認好他們後續的製程條件為何也是很重要的事 ⚠️。有時我們也會主動提供完整的 DRC 請客戶設計時先 Follow 該準則,DRC 不是只提供平面的數據,連縱橫深寬比都是需要考慮進去的。

- 光罩(Tape-out)與 PCM 設計:接下來就是光罩 Tape-out 🎞️,也就是 Design 已經確認好了,必須由我們廠內提供定版下來的光阻 Tone 別、還有 Bias...等數據給 Layout team。光阻 Tone 別搞反,就會導致最終做出來的圖形完全相反 😱(例如原本是要開大洞,結果變成留一個布丁形狀的光阻 🍮);而 Bias 下錯,則是你製作出來的 CD 大小會完全與客戶預期的不同。同時,也需要根據預計要做的製程 Layer 設計該產品的 PCM(電性監控圖案) 🔬,藉由 Pattern 去推測 Die 實際設計的狀況。

- Route(Process flow)串接:中間接下來就是 Route 的串接 🔗。如果對於製程不夠熟在這一步會很痛苦,尤其是接到新開發案時,你會不知道怎麼下手。客戶通常這時也會發送製程需求進來,你要了解到該製程會讓晶圓整體結構出現什麼變化(例如 Open ratio 如何、對整體變化是否大),因此又會牽涉到搭配的光阻厚度...等問題 🤯。這時候就很靠經驗上的累積。

- 防範 Hold Lot:Route 串完後,若有新需求可能會需要有新的製程 Recipe,就要趕快跟各製程窗口聯絡提出需求 📞,並在到貨前一定要確保有該 Recipe,否則會出現 Hold lot 的狀況 🛑。Hold 住對於 wafer 本身是小事,但身為產品 Owner 跟客戶約定的交期是要盡量達成的,中間出現 Low tech 的 hold lot 導致交期延後,有可能會引來客訴...😨

- 量測與專案分類:剩下的就是看 NPI 產品開跑時有無出現意外,開發/整合工程師會使用 OM、SEM、EDX 等量測機台也是家常便飯 🔬。純開發案會分為「客戶需求」以及「CIP」兩種 📁。客戶案子常會跟你要進度及實驗建議;CIP 比較像是建構在已有的製程上去再做優化調整 📈,通常比較是廠內需求,開發方向更能由自己主導。

看到這邊大概就能知道說,為何網路上會說製程整合的完整訓練週期至少是三年了吧... 😅

- Trouble shooting(解 Issue):這比較像是隨機觸發的任務 👾。有時候可能機台跑掉,或是以為跟以往製程沒太大差異的產品結果發現了問題。個人覺得在找 Root cause 的時候其實也滿困難的 🕵️♂️,因為突然穩定的東西出現原因,要找出因子比開發新製程又來的難一些。

三、人際關係很重要 🤝

在開發整合的單位最重要的是:你不是那個親自操作製程機台的人。你都是整合了,怎麼可能每種製程機台都是要你親自下貨調整參數呢?🤷♂️ 這也是為何在徵選人時會希望是「邏輯清楚會溝通的人」來擔任此職位,因為很明顯的是需要擔任公司與客戶之間的橋樑 🌉。當你在做新案子開發時,少不了要跟各單位合作,且工程師直接對到該單位的主管都是家常便飯。若一不小心出現溝通上的誤解,造成對方評價對你的下降,其實在公司內部會出現不好的現象,而你以後的專案推動上會增加困難 🚧。態度上就算你是演的,也要展現你的積極度 🔥。

四、產品進入量產 🏭

產品其實要進入到量產會需要經過很多階段去驗證,而一個型號從開發工程師到量產整合工程師手上,是需要經過很多會議以及流程去審查的 📑。通常進量產前會先投片好幾筆貨作為 Pilot,此時的製程條件基本上是固定,材料來源也要固定,不可以有任何變動 🚫,而可以變動的會是製程機台。這邊的變動是指為了確保機群都可以有差異不大的製程穩定性,甚至會故意指定哪幾筆要去那些機台做貨 📊。最終會根據這些貨去計算所謂的製程能力 Cpk、Ppk,並確認 SPEC 定義的合理性,而製程能力指標不佳的也要找出原因為何,要在會議上解釋清楚 🗣️。而這階段的會議就是所謂的 OK to Fab APQP 會議,若進入量產有任何問題,都有可能被停線或是被退回開發工程師手上都有可能的 🔙。

番外篇:根據各公司的常見差異 🏢

- 量測機台管理:有些公司整合工程師會同時肩負管理量測機台(如:CD-SEM)的責任 📏。但有些公司同時要兼任 Recipe 設定的責任,也有公司會有獨立的量測 Team,也有公司是每個製程單位都有負責管理的量測機台。

- 值班制度:有些公司的整合會需要值班 🌙,常見一般工作天都是排班至小夜,大夜通常交給副工程師/助理工程師處理一些有 SOP 可以 Follow 的事項。假日也會有排班 🗓️,主要是讓單位所屬的貨物可以在非平日上班時間也可以順暢過貨。有些公司則是未有值班安排,可能會有常駐的值班團隊進行 On call 通知貨主貨況跟異常 📱。

以上算是我工作上的主要框架,僅提供參考,不保證有用 🤣。