CPU 介紹

(1). 指令集 (Instruction set): 依據 CPU 功能或目標制定 (EX: ADD or SUB)

(2). 暫存器 (Register set): 支援程式碼或指令的擷取與執行

(3). 算術邏輯運算單元 (ALU): CPU 的運算單元

(4). 控制單元 (CON): 控制單元接受到指令後,產生控制訊號,達成暫存器間的資料傳輸

(5). 記憶體定址與輸入輸出 (Memory addressing and I/O processing)

CPU doesn’t control I/O devices, it communicates with them.

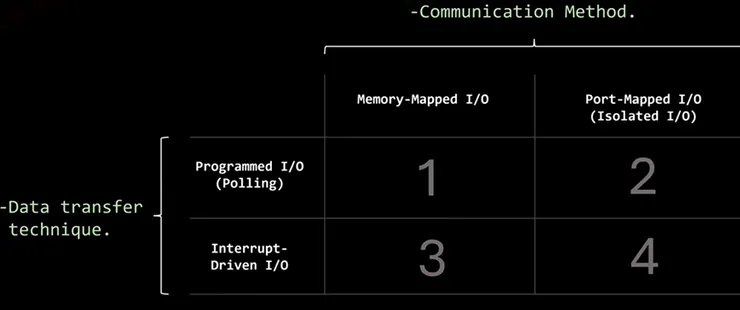

About I/O need to think about

- Communication method ( MMIO & Isolated I/O )

重點: How CPU physically talks to devices?

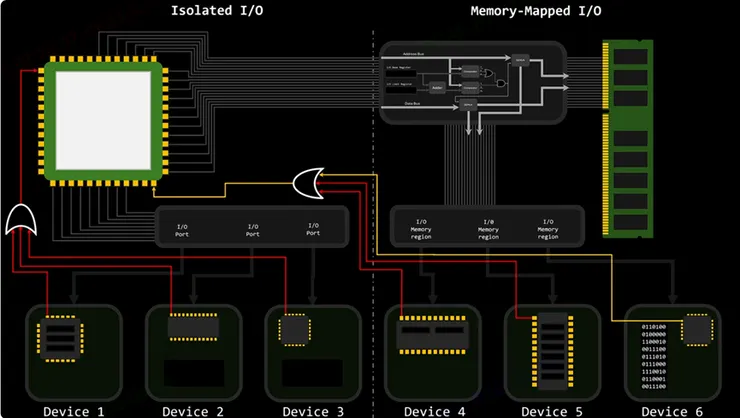

X86 架構 (CISC: Complex Instruction Set Computer),有 Memory-Mapped I/O & Isolated I/O

ARM 架構 (RISC: Reduced Instruction Set Computer),只有 Memory-Mapped I/O

- Data transfer technique ( Polling & Interrupt Driven I/O )

重點: How and when the data moves?

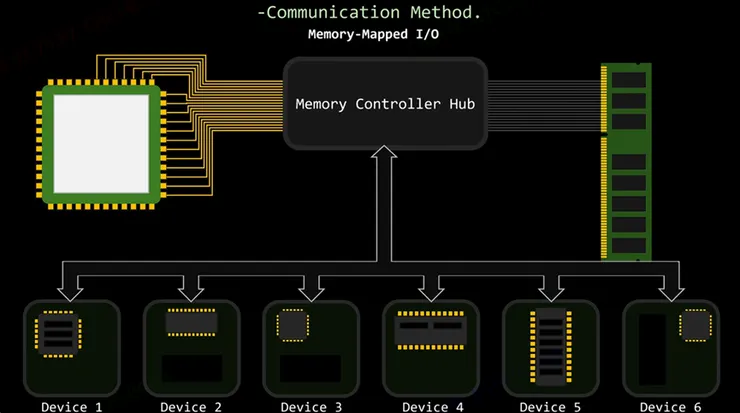

1. 記憶體映射 I/O (Memory-Mapped I/O, MMIO)

- 概念:將 I/O 裝置的暫存器直接映射到 CPU 的記憶體位址空間中。

- 運作:CPU 像讀寫一般記憶體一樣(使用 LOAD / STORE 指令)來存取裝置。

- 優點:不需特殊指令,程式撰寫簡單。

- 缺點:會佔用部分記憶體位址範圍。

· 現況:現代處理器(如 ARM、Apple Silicon、RISC-V)幾乎只使用 MMIO。

· 原因:現在的 64 位元位址空間非常龐大,不需要擔心佔用記憶體空間的問題。使用 MMIO 可以直接利用一般記憶體指令(如 MOV)來控制硬體,速度更快且開發更容易。

· 例外:只有 x86 架構(Intel/AMD)為了相容幾十年前的舊硬體,還保留了「埠映射 I/O (PMIO)」,但即使在 x86 上,現代高效能裝置(如顯卡、NVMe SSD)也幾乎都轉向 MMIO 了。

2. 埠映射 I/O (Port-Mapped / Isolated I/O)

- 概念:I/O 裝置擁有獨立於記憶體的位址空間(稱為 I/O Port)。

- 運作:CPU 必須使用專門指令(如 x86 的 IN 和 OUT)來與裝置溝通。

- 優點:不佔用記憶體空間,位址解碼較簡單。

- 缺點:指令集變得複雜,硬體邏輯較多。

------------------------------------------------------------------------------------------------

3. 程序控制 I/O (Programmed I/O / Polling)

- 概念:這是一種軟體主導的資料傳輸方式。

- 運作:CPU 會不斷地詢問(Polling)裝置:「你準備好了嗎?」直到裝置回應已完成。

- 優點:實作最簡單,不需要額外硬體支援。

- 缺點:極度浪費 CPU 效能,因為 CPU 在等待 I/O 時無法執行其他任務

在特定場景下才比較強

· 極高速裝置:例如現代的超高速 NVMe SSD 或萬兆網卡。因為處理一個「中斷」需要儲存/回復 CPU 暫存器(Context Switch),這個開銷有時比直接 Polling 還慢。在高效能驅動程式(如 SPDK/DPDK)中,會刻意用 Polling 來追求極限低延遲。

· 簡單嵌入式系統:在沒有作業系統(Bare Metal)的小型微控制器上,為了省電或程式碼簡單,Polling 依然常見

4. 中斷驅動 I/O (Interrupt-Driven I/O)

- 概念:這是一種硬體通知的傳輸方式。

- 運作:CPU 下達指令後就去忙別的事。當裝置準備好資料時,會發出一個中斷訊號 (Interrupt) 通知 CPU 回頭處理。

- 優點:CPU 利用率高,不需在原地空等。

缺點:硬體設計較複雜,且如果中斷太頻繁,頻繁切換任務(Context Switch)也會產生開銷。

切記: I/O device isn’t memory, can behave like memory but not ideal

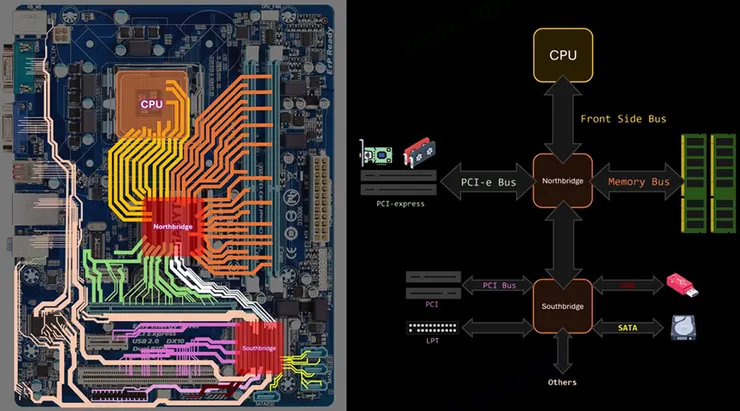

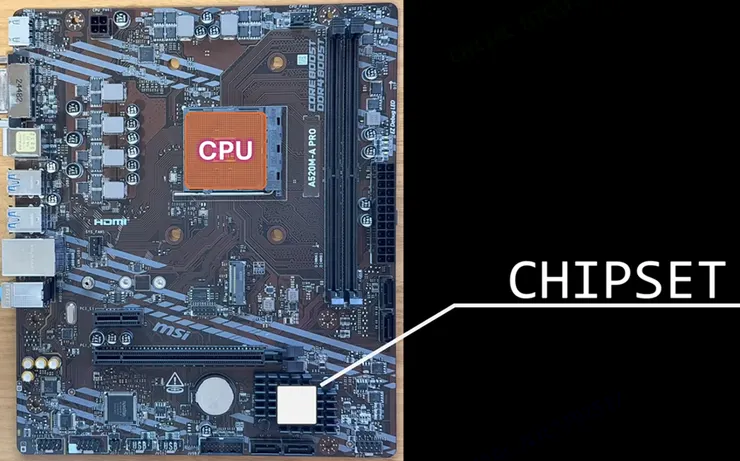

過去有南橋晶片 & 北橋晶片(示意圖如下)

但是 CPU 越來越快,南橋 & 北橋晶片整合進 CPU,只留下 ChIPSET

最後

Question: 既然都可以直接連到 CPU,為什麼設計時還是採用 Memory-Mapped I/O, MMIO 非 Port-Mapped / Isolated I/O ?

ANSWER: Each IO device was mapped to a specific memory region But each manufacturer decided on their own layout This mapping was hardwired into motherboard It couldn’t be reconfigured through software