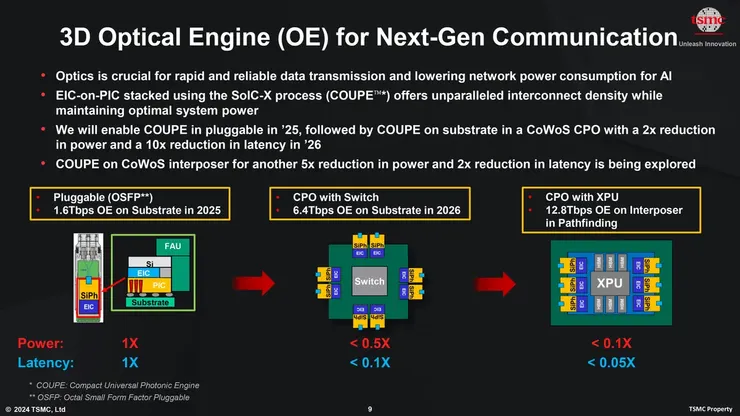

COUPE 的核心,在於透過 SoIC-X 製程將電子 IC(EIC)與光子 IC(PIC)進行 3D 堆疊鍵合,打造出高密度的光電整合引擎。這代表光不再只是外掛模組,而是被直接拉進晶片封裝架構之中。 圖中其實呈現了一條清晰的演進路徑。第一階段是 2025 年的可插拔光模組(OSFP)形態,光引擎仍位於基板層級,屬於較保守、可替換的整合方式。第二階段則在 2026 年進入 CoWoS CPO 架構,光電單元與交換晶片同封裝,功耗與延遲顯著下降。最後,更進一步探索將光引擎整合至 CoWoS interposer,甚至 XPU 內部,讓光成為核心封裝的一部分。

最近市場談到矽光子,多半聚焦在光模組如何貼近 ASIC,或 Nvidia 展示的 CPO 交換器。畫面裡是光纖、微型引擎、交換晶片,焦點幾乎都落在光元件本身。

但如果把技術資料攤開來看,TSMC 的 COUPE 其實不是一顆光模組,也不是單純的矽光子製程。它真正試圖改寫的,是封裝架構的邏輯。COUPE 是 Compact Universal Photonic Engine 的縮寫。Compact 代表它必須小型化到可以進入先進封裝內部;Universal 意味著它不是客製化模組,而是可被不同系統採用的通用架構;Photonic 指向矽光子整合;Engine 則強調它是一個可被系統調度的光電單元,而非單一元件。

光子技術其實已經成熟,問題在「怎麼進封裝」

從矽光子平台技術來看,關鍵元件幾乎都已經成熟。單晶片可以整合高速調變器、光偵測器、被動波導與耦合結構,只差光源仍需異質整合。在 300mm 晶圓上整合上萬個光元件也不是問題。換句話說,光子技術本身並不是瓶頸。

真正的瓶頸,是高速 AI 系統的 I/O 功耗。資料中心的頻寬需求持續上升,電訊號在 PCB 與封裝中的損耗在 200Gbps 等級已變得難以承受。電的極限正在逼近,光成為幾乎唯一可行的解法。

問題於是轉化成另一個層次:光要怎麼進入 GPU 的先進封裝,而不是停留在外部模組?這正是 COUPE 出現的背景。

COUPE 真正做的是光電鍵合

COUPE 的核心是利用 TSMC SoIC face-to-face 技術,把電子 IC 與光子 IC 直接鍵合在一起。它結合 TDV 結構、嵌入式微透鏡與金屬反射層,讓光耦合可以在晶圓級完成。

這個設計的重點並不只是光效率,而是三個條件:可堆疊、可量產、可被封裝。

COUPE 的規格,例如 10 微米對位容差、0.3dB 垂直耦合損耗、低損耗 SiN 波導,以及 wafer-level 共振波長控制,其實都在回答同一個產業級問題:光能否成為可標準化的封裝單元,而不是高風險客製模組。

這讓光電單元第一次具備了 Chiplet 化的條件。

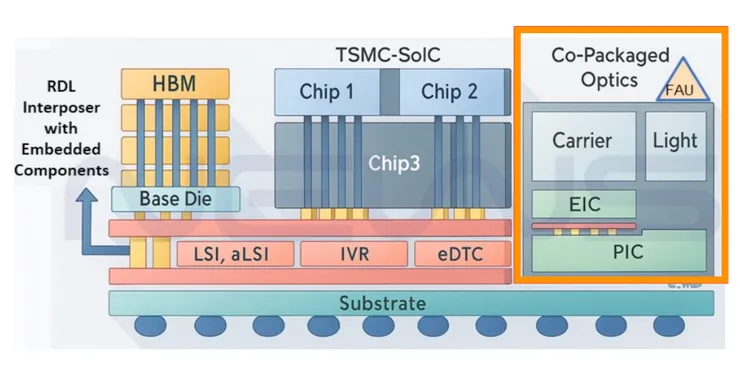

當 COUPE 進入 CoWoS,封裝角色開始轉變

在 COUPE 與 CoWoS 的整合示意圖中,可以清楚看到光電引擎被納入先進封裝結構之中 Co-Packaged Optics。

原本 CoWoS 的價值在於大面積 interposer 與 HBM 整合,解決的是電訊號的高頻寬互連問題。但一旦光電單元內嵌其中,封裝層就不再只是電互連平台,而成為電光混合基礎設施。

封裝的定位從「高階載板」升級為「系統控制中心」。

目前矽光子封裝仍面臨良率與耦合挑戰 Co-Packaged Optics。測試良率波動大,光纖耦合損耗不穩定,封裝複雜度高。這使得市場仍然偏好外接模組,因為責任邊界清楚。

但如果光電鍵合發生在晶圓級流程內,核心價值就會集中在具備 SoIC 與先進封裝能力的廠商身上,而不是傳統模組組裝廠。

COUPE 的意義不在於短期出貨量,而在於替下一代 AI GPU 世代預先畫好架構邊界。當頻寬再翻倍,功耗再翻倍,光不再是優化選項,而是基礎條件時,封裝將成為光電整合的主戰場。

那時候,討論的就不再是「誰的光模組效率比較好」,而是「誰定義了光在封裝中的位置」。