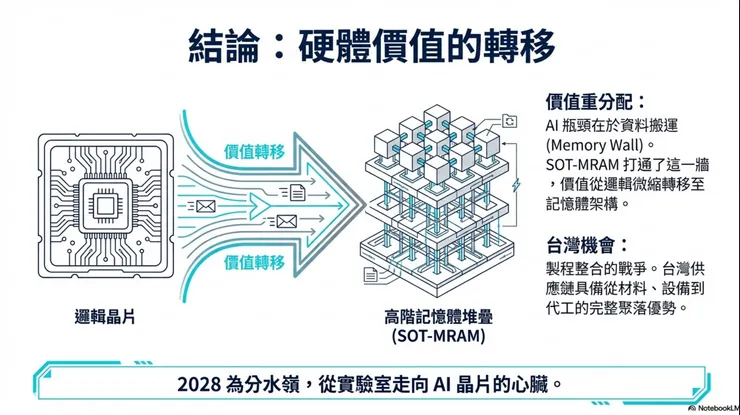

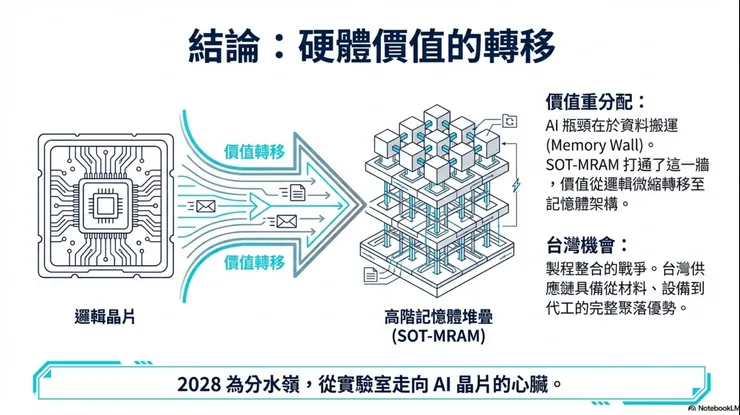

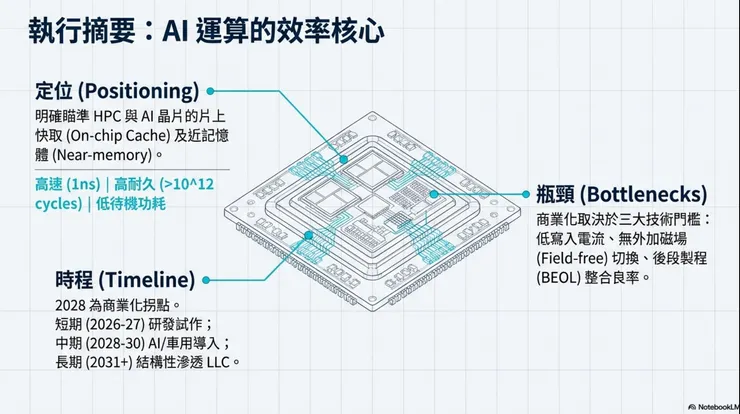

執行摘要

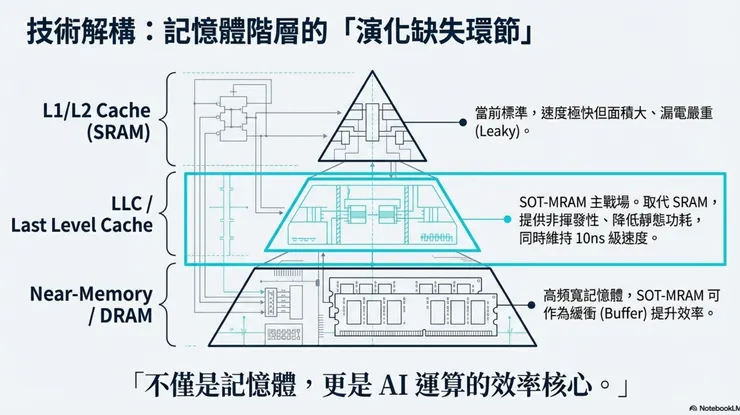

SOT‑MRAM(Spin‑Orbit Torque MRAM)在「高速、耐久、低待機功耗」的潛力上,明確瞄準高效能運算(HPC)與 AI 晶片的片上快取/近記憶體(near‑memory)需求,但其商業化節奏仍高度取決於三個技術瓶頸:低寫入電流、可靠的無外加磁場(field‑free)切換、以及後段製程(BEOL)整合良率與成本。

過去三年(2023–2026)關鍵訊號偏正向:研究端已出現接近產品規格的「小容量陣列」展示,例如在 2023 IEDM 上,台灣團隊提出 SOT‑MRAM 陣列晶片並主張其功耗可降至對照 STT‑MRAM 產品的 1%,並示範約 10ns 等級速度; 2025 年更有 Nature Electronics 64kb 陣列整合 CMOS 控制電路、1ns 切換與 >10 年穩定性等成果(官方摘要)。 同期,歐洲研究機構也展示 <100 fJ/bit 寫入能耗、>10^15 耐久與 300mm 製程可擴充性的實驗結果,明確鎖定「LLC 取代 SRAM」情境。核心判斷是:短期(1–2 年)SOT‑MRAM 仍以研發/試作與少量客戶驗證為主,投資影響主要反映在「先進製程模組能力與研發生態系」;中期(3–5 年)若能在量產線上交付「可設計的 PDK/記憶體宏單元 + 可控良率」,將開始出現由少數 AI/車用平台導入的拐點;長期(5 年以上)才有機會在更多 HPC/AI 產品線中形成結構性滲透。

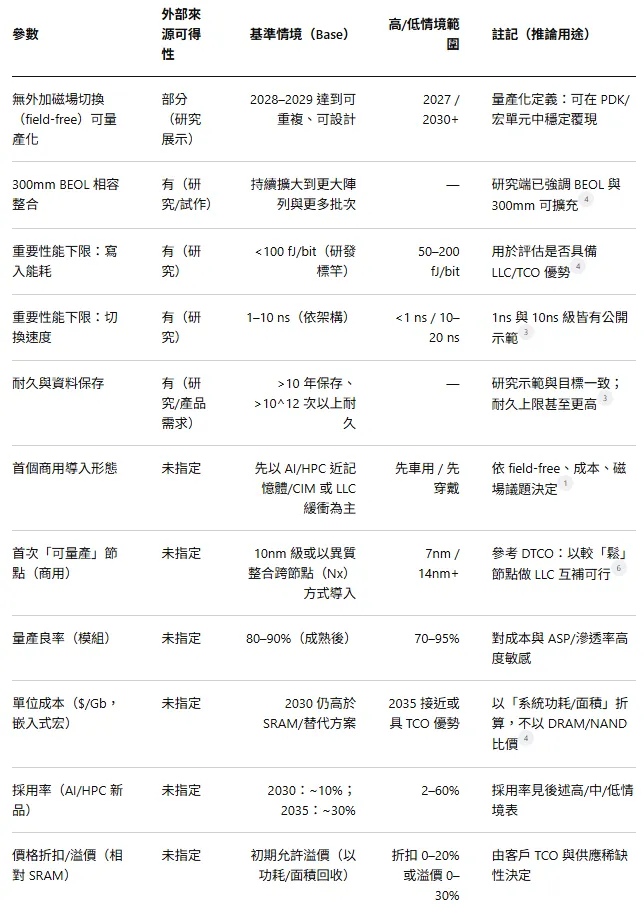

關鍵假設與分析框架

本報告以 2026/02(台北時間)為基準,將短/中/長期分別定義為 2026–2027 / 2028–2030 / 2031–2035,並以「技術成熟度(TRL)→ 試產/量產節點 → 應用採用率 → 市場規模 → 供應鏈分配」自上而下推演。

下表列出用於推論的關鍵參數;凡外部來源未提供可直接引用的量產數字者,一律標註「未指定」,並以情境假設補足(供估算,不等同事實預測)。

關鍵參數與假設表(含未指定項)

以上「已公開驗證」的性能/陣列里程碑主要來自:SOT‑MRAM 技術綜述(指出瓶頸與 BEOL/field‑free 議題)、300mm 可擴充的研究展示、台灣團隊 64kb 1ns/ >10 年成果,以及 DTCO 對 LLC/面積縮放的可行性分析。

技術與量產路線

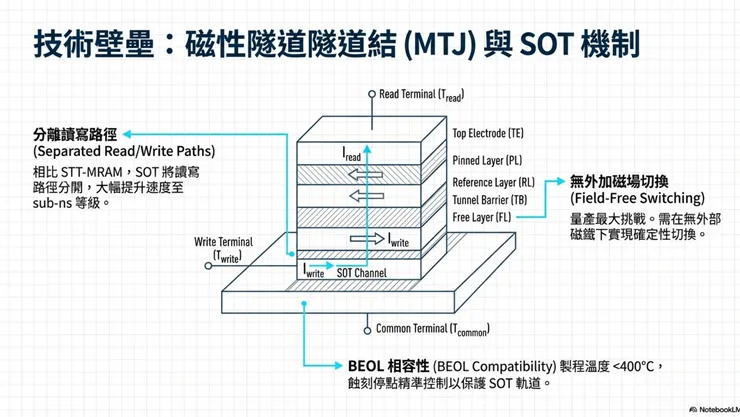

SOT‑MRAM 的價值主張在於分離讀寫路徑、降低待機功耗並追求 SRAM 級速度;但 3‑terminal 架構的面積/佈線成本、寫入電流與 field‑free 的可製造性,是從「論文數據」走向「可設計產品」的主戰場。

三期技術成熟度與量產/試產節點

短期到中期的「里程碑可信度」已有一些客觀支撐:一方面,台灣產學研在 2023–2025 連續展示 SOT‑MRAM 陣列晶片與 64kb 等級陣列整合 CMOS,並指向 1ns 與 >10 年保存; 另一方面,歐洲研究機構以 300mm 晶圓實驗驗證能耗與耐久上限,明確為 LLC 場景服務。

技術商業化流程圖(示意)

材料/堆疊(spin‑Hall/β‑W 等)

→ BEOL 相容整合(400°C 熱預算、蝕刻停點、良率視窗)→ 記憶體宏單元/PDK(版圖規則、感測放大器、ECC/修復)→ 客戶試片/樣品(PPA 與系統 TCO 驗證)→ 可靠度/車規(溫度、擾動磁場、資料保存與耐久)→ 量產爬坡(良率 + 成本曲線)

此流程中,「BEOL 蝕刻停點控制」與「field‑free 的可縮放性」被反覆點名為整合難點;同時也出現透過幾何/材料工程、BEOL selector、以及 DTCO 方式降低面積與能耗的路徑。

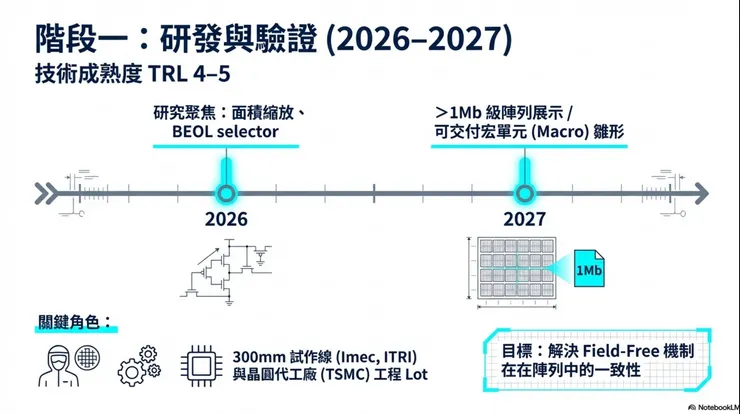

里程碑時間軸

(2024–2026 為已發生/已公開;2027–2035 為本報告推估,供投資假設監控)

- 2024:SOT‑MRAM 陣列晶片公開(CIM 架構、功耗對照與 10ns 級速度)

- 2025:Nature Electronics 64kb SOT‑MRAM(整合 CMOS 控制電路、1ns、>10 年保存)

- 2026:研究/DTCO 持續聚焦「面積縮放、BEOL selector、LLC 規格」

- 2027(推估):>1Mb 級陣列展示增多;開始出現「可交付宏單元接口」雛形

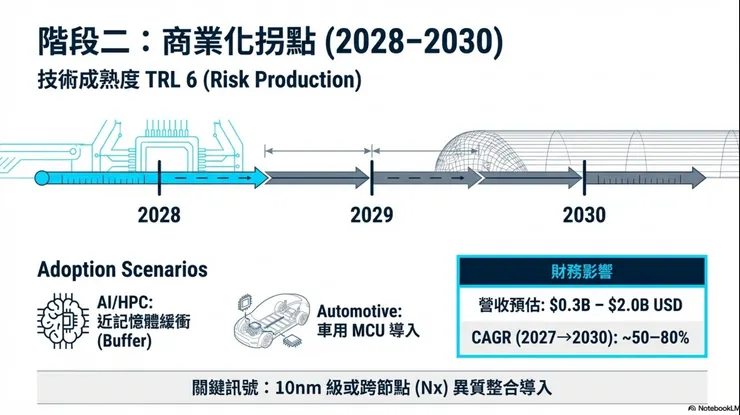

- 2028(推估):少數客戶以工程 lot 方式導入(AI/edge‑AI/CIM 特定晶片)

- 2029(推估):若良率與 field‑free 定型,進入小量量產;嵌入式新型 NVM 市場同步放大

- 2030(推估):部分平台形成可複製導入模式;embedded emerging NVM 市場規模接近數十億美元(外部研究)

- 2031–2032(推估):HPC/AI 的 LLC/緩衝應用開始擴散到更多客戶

- 2033–2035(推估):若面積/成本逼近 SRAM 或在系統 TCO 更優,滲透率進入結構性成長期

需求滲透情境與市場規模

需求端要讓 SOT‑MRAM「從亮點變標配」,通常需要同時滿足兩個條件:

第一,應用場景存在明確痛點(SRAM 漏電/面積、Flash 在 ≤28nm 節點缺乏成本有效解);第二,供應端能提供可設計、可量產且成本可預期的模組/宏單元。

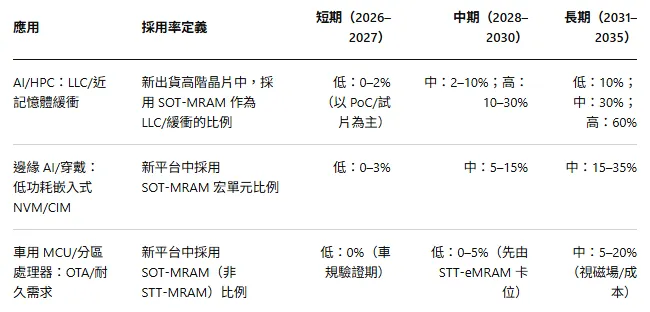

主要應用與高/中/低採用率情境(本報告假設)

AI/HPC 為最優先的滲透方向,原因在於研究端已直接以「取代 SRAM LLC」為靶心,並提出 sub‑ns、低能耗與高耐久的數據,且以 DTCO 方式討論面積縮放與跨節點整合(例如以 BEOL selector 降低 10–40% bitcell 面積,並用 LLC 可接受的 retention 規格重新平衡寫入電流)。

車用端短期更可能先由嵌入式 MRAM(多為 STT‑eMRAM)推進:例如已公開的 16nm FinFET 車用嵌入式 MRAM 方案主打快速更新(例:20MB 程式碼約 3 秒 vs Flash 約 1 分鐘)、高耐久(~百萬次更新循環)與高溫保存(150°C、20 年)等,符合 OTA 與軟體定義車趨勢。 因而在買方框架下,SOT‑MRAM 在車用的「接棒時間」多半晚於 AI/HPC,除非 field‑free 與磁場/成本問題提前解決。

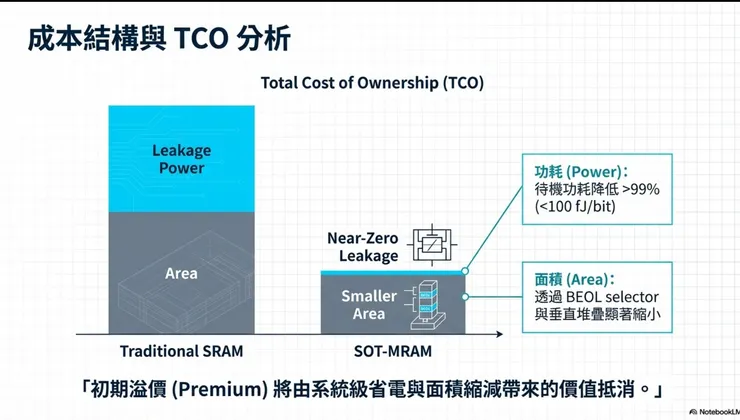

成本與價格趨勢(方向性判断)

SOT‑MRAM 成本曲線的兩個主變數是「面積密度」與「BEOL 整合製造成本」。一方面,研究端已指出 SOT‑MRAM 有潛力在高密度下比 SRAM 更低待機功耗,且可透過縮放 SOT track 或導入 BEOL selector 等方式改善面積/能耗; 另一方面,技術綜述亦明確指出 SOT‑MRAM 相較 STT‑MRAM 在整合上更敏感(例如蝕刻停點需避免傷及極薄 SOT track),意味著早期量產的報廢/良率折損可能拖累成本下行速度。

結論是:2028–2030 更可能採「價值定價」而非「每 bit 比價」(以省電/面積換取整體 TCO),而 2031–2035 才有機會在面積與良率成熟後,走向類似 eNVM 模組的規模經濟。

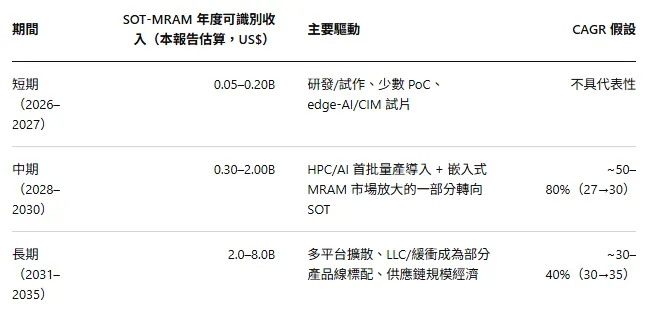

市場規模估算與 CAGR 假設(表格)

本報告採兩段式估算:

(1) 以外部研究對「embedded emerging NVM」與「stand‑alone emerging NVM」的規模作為可見天花板/地板;

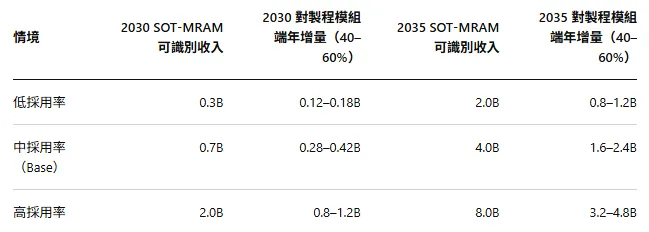

(2) 再以「SOT 在 MRAM 中的滲透」與「HPC/AI cache 額外增量」形成 SOT‑MRAM 的可識別收入區間(多數為模組/宏單元與製造服務的價值)。外部研究顯示:embedded emerging NVM 2024 僅約 1.42 億美元、2030 約 32.6 億美元(其中 2030 MRAM 約 24%); 且 stand‑alone memory 市場中「Emerging NVM」在 2030 仍僅約 4 億美元量級,顯示結構性增量更偏向「嵌入式/系統整合」而非獨立顆粒。

註:上述為「SOT‑MRAM 可識別價值」的範圍估算,核心不確定性來自:是否真正切入 LLC,以及量產良率與單位成本下降速度。研究與外部產業報告僅能支持「方向」與「天花板/地板」:例如嵌入式新型 NVM 市場 2023→2029 的高速成長(至 26 億美元)與 wafer volume 擴張,以及 ≤28nm 節點缺乏成本有效 eFlash 的結構性驅動。

供應鏈受惠與投資影響

SOT‑MRAM 的價值鏈條,通常由「晶圓代工/IDM 製程模組」攫取最大份額,其次是磁性材料/薄膜沉積與蝕刻/量測設備(資本支出),以及記憶體宏單元/IP 生態系(較小但具黏性)。

供應鏈受惠廠商清單(台灣/國際)

說明:此表為「可能受惠」名單,並非代表該公司已量產 SOT‑MRAM;分類邏輯以產業位置(製程模組、應用導入、研究/市場)為主。

外部公開資訊亦顯示:先進節點缺乏成本有效的嵌入式 Flash,正在推動主要 foundry 與 IDMs 投資 eMRAM/ePCM/eRRAM,並將 eNVM 往 10nm 級推進;同時 embedded emerging NVM 的 wafer volume 與市場規模在 2023–2029 可能呈現高速成長。

情境化財務影響摘要(粗估)

以下以「SOT‑MRAM 年度可識別收入」為基礎,假設價值分配:晶圓代工/IDM 製程模組 40–60%、IP/設計服務 5–15%、其餘反映在設備/材料的資本支出循環(不等同當期營收)。此分配為本報告假設(未指定)。

買方含意:短期(1–2 年)財務貢獻仍偏「研發費用/技術選配」;但若中期(3–5 年)能跑通「宏單元 + 可靠度 + 良率」閉環,製程模組端的增量收入具備從 10^8 美元級走向 10^9 美元級的選擇權。

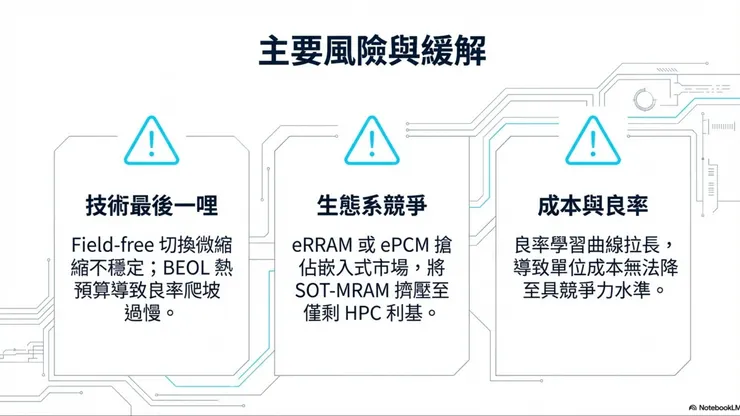

主要風險與緩解策略

最重要的風險仍然是技術與製造的「最後一哩」:field‑free 切換若無法在縮放後穩定成立,或 BEOL 整合(薄 SOT track 的蝕刻停點/熱預算)導致良率學習曲線拉長,將直接延後商業化時間並壓縮投資報酬。

第二層風險是生態系與替代方案競爭:在嵌入式 NVM 戰場,eMRAM/eRRAM/ePCM 同時推進,且外部研究預期 MCU 將成為 embedded emerging NVM 最大收入來源;若 SOT‑MRAM 的成本/面積拐點晚於其他方案,SOT 可能被迫退回較小的利基(特定 HPC/AI)。

緩解策略可聚焦三件事:其一,以 DTCO/BEOL selector 等路線持續降低 bitcell 面積與寫入電流;其二,優先鎖定願意為「待機功耗/面積」付費的 HPC/AI 客戶,建立可複製的導入模板;其三,在車用導入上採「先 STT‑eMRAM、後 SOT‑MRAM」分段式路線,避免車規/磁場風險一次到位。

監測KPI

- 升評:具備先進製程整合能力與客戶黏著度的「製程模組/晶圓代工核心供應者」。理由是 SOT‑MRAM 的價值多數體現在「製程模組選配、良率學習、以及與客戶共同定義宏單元」,屬於強者恆強的工藝護城河;且既有 eMRAM 量產與車用導入進度可作為現金流與學習曲線的緩衝。

- 中性:獨立 MRAM/新型 NVM 概念股與純 IP 模式。理由是 SOT‑MRAM 的主戰場可能在「嵌入式/SoC 內生」而非 stand‑alone 顆粒,外部資料也顯示 stand‑alone emerging NVM 到 2030 仍偏小;因此短期股價催化多由技術新聞驅動、基本面可見度較低。

- 降評:若投資標的之競爭優勢主要來自「嵌入式 Flash」且缺乏 ≤28nm 的替代路線或客戶轉換能力,則在 embedded emerging NVM 加速導入下可能面臨結構性壓力(依個股而定)。

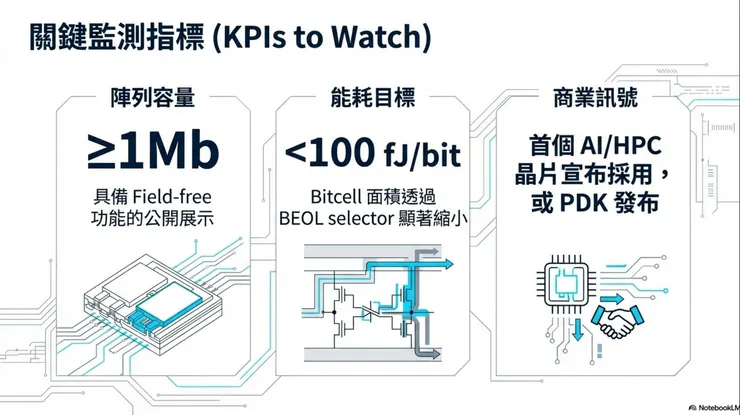

三個可追蹤的量化 KPI(用於驗證本報告假設)

- 可公開驗證的 SOT‑MRAM 陣列容量里程碑:≥1Mb(或更大)且同時滿足(a)field‑free、(b)BEOL 相容熱預算、(c)良率/錯誤率可量化(例如 ppm 級)──每年追蹤公開論文/會議/客戶樣品披露趨勢。

- 能耗與面積縮放指標:公開數據中「寫入能耗(fJ/bit)」與「bitcell 面積相對 SRAM(%)」的年度改善幅度;特別關注是否能透過 BEOL selector/DTCO 逼近或匹配先進節點 SRAM 的面積標竿。

- 製程生態系商用化信號:是否出現「可設計的 PDK/宏單元」與「risk production/量產節點」的公開里程碑(例如車用或 AI 平台的實際出貨/樣品時程);可用嵌入式 MRAM 新平台(如車用 16nm eMRAM)之樣品與量產節奏作為先導指標。