宇川精材(U-Precision Materials,股票代號:7887)是台灣半導體材料在地化供應鏈中的關鍵廠商,特別是在進入 2nm 及更先進製程的節點上扮演重要角色。

原子層沉積(Atomic Layer Deposition, ALD)是什麼?是當後半導體邁入 2 奈米、GAA 架構以及 HBM 記憶體製程中最關鍵的薄膜生長技術。簡單來說,如果傳統的化學氣相沉積(CVD)像是用「噴漆」把油漆噴在牆上,那麼 ALD 就像是**「貼貼紙」**——它能確保每一層薄膜都精準地以「原子」為單位,一層一層均勻地鋪滿所有複雜的表面。

一、 ALD 的工作原理:四步驟循環

ALD 的核心在於其**「自我限制(Self-limiting)」**的表面化學反應。它將反應過程拆解成四個重複的循環步驟:

1. 注入第一種前驅物(Pulse A):

氣態的前驅物進入反應室,與晶圓表面發生化學反應。因為是「自我限制」,一旦表面所有的反應位點都被佔滿,多餘的氣體就不會再反應。

2. 清洗(Purge):

使用惰性氣體(如氮氣或氬氣)將反應室內剩餘的前驅物和反應副產品排空,只留下表面那層單分子厚度的化學物質。

3. 注入第二種前驅物(Pulse B):

第二種氣體進入,與表面已吸附的物質發生反應,形成目標薄膜(例如氧化鋁或金屬層)。同樣地,這步也會在表面飽和後停止。

4. 再次清洗(Purge):

清空多餘氣體,完成一個原子層的沉積。

關鍵特性: 透過重複這四步循環,ALD 可以精確控制薄膜的厚度(循環次數 x 原子層厚度)。

二、 ALD 的核心優勢

相較於物理氣相沉積(PVD)或化學氣相沉積(CVD),ALD 擁有無可取代的優點:

• 極佳的包覆性(Conformality):

不論晶圓表面有多深、多窄(高深寬比),或是像 GAA 那樣立體的結構,ALD 都能確保「轉角處」與「底部」的薄膜厚度完全一致。

• 原子級精度:

厚度控制精準到奈米以下,這對於 2nm 以下製程控制漏電至關重要。

• 無孔隙、高純度:

層與層之間接合緊密,能形成高品質的電絕緣層(High-K)或金屬導體。

三、 為什麼 ALD 在現在如此重要?

隨著半導體製程微縮,ALD 已從「選配」變成了「必備」:

1. 先進邏輯製程(GAA 結構)

在 2 奈米以下,電晶體結構從 FinFET 轉向 GAA (Gate-All-Around)。閘極(Gate)必須完全「環繞」通道(Channel)。在如此狹小的縫隙中,只有 ALD 這種具備「非方向性」的技術,才能均勻地把電介質層與金屬閘極鋪滿在通道四周。

2. 高頻寬記憶體(HBM)

HBM 的核心是 TSV(矽穿孔) 技術,需要在矽片上鑽出極深的孔隙。為了確保這些深孔內壁具備良好的絕緣特性,必須使用 ALD 來沉積絕緣層,避免訊號干擾或短路。

3. 3D NAND Flash

隨著 Flash 堆疊層數超過 200 層甚至 300 層,結構的縱深比極高,傳統技術無法將化學品均勻送達底部,ALD 是維持良率的唯一解答。

總結:產業鏈的價值點

對於像宇川精材這類公司,他們提供的就是 ALD 循環中第一步與第三步所需的「化學藥水」(前驅物)。

關鍵挑戰: ALD 的缺點是沉積速度慢(Throughput 低)。因此,產業界現在正努力開發能在單一腔室內同時處理多片晶圓的設備,這也意味著對前驅物材料的消耗量將會隨著產速提升而大幅增加。

在半導體材料的領域中,ALD 前驅物(Precursors) 被稱為「奈米級的煉金術」,其難度不僅在於化學合成,更在於如何在極端條件下維持精確的物理特性。

對一家像宇川精材這樣的公司來說,要跨過這道門檻,主要面臨以下五大技術與商業挑戰:

一、 矛盾的化學特性:揮發性與熱穩定性的平衡

前驅物必須像個「聽話的快遞員」,既要跑得快(揮發性),又不能在中途累倒(熱穩定性):

• 高揮發性(Volatility): 為了進入 ALD 反應室,前驅物必須在相對低溫下轉化為氣態。

• 熱穩定性(Thermal Stability): 在輸送管路與進入反應室(通常在 200 °C 至400 °C )的過程中,分子結構不能提前崩解。如果提前分解,就會變成不均勻的 CVD(化學氣相沉積),導致膜厚失控。

• 難度: 通常揮發性強的分子結構較不穩定,要找到同時兼具兩者的配體(Ligands)組合,需要極強的分子工程研發實力。

二、 分子配體(Ligand)的設計障礙

前驅物由「中心金屬原子」和「圍繞它的配體」組成。配體的設計決定了 ALD 最核心的「自我限制(Self-limiting)」特性:

• 反應位點佔位: 配體必須在反應發生後,精準地覆蓋在表面,防止後續的相同分子再貼上來。

• 副產物排除: 反應後的配體殘餘(副產物)必須是氣態,且能被輕易沖洗(Purge)乾淨。

• 技術障礙: 如果配體設計不好,會殘留碳、氫或鹵素在薄膜中,形成雜質,導致導電性差或漏電。

三、 零容忍的純度要求:6N+ 的極限

在 2 奈米或 A16 製程中,任何一個微小的金屬離子雜質都可能導致整個晶圓報廢。

• 純度門檻: 目前先進製程要求純度需達 6N(99.9999%) 甚至 7N。

• 痕量分析: 雜質含量必須控制在 ppb(十億分之一) 甚至 ppt(兆分之一) 等級。這意味著連生產設備、充填鋼瓶的內壁材質(通常需特殊電解拋光),都不能有原子掉落。

• 難度: 宇川精材法說中提到的「超微量分析實驗室」和「鋼瓶清洗分裝技術」,就是為了克服這個門檻。

四、 安全與儲運:自燃與毒性的挑戰

許多高性能的 ALD 前驅物(如 Al(CH_3)_3 或高活性矽源)具有極高的危險性:

• 自燃性(Pyrophoric): 接觸空氣即起火。

• 反應性: 遇水即爆炸或釋放劇毒氣體。

• 難度: 廠房的特殊防爆設計、氣體輸送系統的密封性,以及對緊急應變的要求極高。這也是為什麼宇川在南科的廠房被強調為「唯一可合法製造處理高危險化學品」的基地。

五、 長達數年的驗證馬拉松(Qual Period)

這是對材料商最折磨的商業障礙:

1. 實驗室驗證(Lab Verification): 材料本身是否達標。

2. 設備端驗證(Tool Matching): 在應用材料(AMAT)或天虹的機台上跑出的數據是否穩定。

3. 客戶端量產驗證(High Volume Manufacturing): 這是最難的一關,台積電等廠會針對「批次穩定性」進行極其嚴苛的測試。

• 難度: 驗證週期往往長達 24 至 36 個月。對於資金管理者而言,這段期間只有研發投入、沒有營收,是非常考驗財務韌性的「死亡之谷」。

總結與洞察

為什麼國際大廠(Merck、Entegris)能領先?因為他們累積了數十年的配體資料庫與專利牆。

宇川精材的難度在於,它必須在這些巨頭的專利夾縫中,開發出不侵權且性能更優的合成路徑,同時還要承擔高昂的建廠資本支出與漫長的驗證期。一旦通過驗證,這種「黏著度」就會轉化為極強的競爭門檻,讓後來者幾乎無法取代。

既然宇川的高階人才多來自台積電與世界先進,這對於縮短「客戶溝通」與「驗證痛點」非常有幫助——因為他們最清楚台積電對於「穩定性」的極端偏執。

以下為宇川核心技術與未來展望的整理:

核心技術:高純度原子層沉積(ALD)材料

宇川精材的核心競爭力在於**高純度有機金屬前驅物(Organometallic Precursors)**的研發與製造。

- ALD 製程專用材料: 隨著半導體邁向 3nm、2nm 甚至埃米(Angstrom)世代,電晶體結構愈發精密,傳統的 CVD 或 PVD 已難以滿足奈米級的厚度控制。宇川專攻的 ALD(原子層沉積) 技術能逐層精準堆疊原子,其生產的前驅物(如 TSA、 TMCTS、TMGa、TMAl等)是確保製程一致性的核心。

- 一條龍整合服務: 具備從材料合成、純化、量產到「鋼瓶清洗與安全管理」的全方位能力。由於半導體級前驅物多屬具高度化學活性的危險品,宇川擁有通過 ISO 17025 認證的超微量分析實驗室,能提供極高可靠度的供應鏈解決方案。

- 全球稀缺供應商: 宇川是全球少數(僅四家)能供應先進製程特定 ALD 前驅物的廠商之一,與 Merck、Air Liquide 及 Hansol 等國際化學巨頭並列,且是其中唯一的台灣本土業者。

未來展望:產能擴張與在地化優勢

宇川目前的發展策略聚焦於伴隨主要客戶(如台積電)的先進製程擴張,其展望主要體現在以下三個層面:

- 南科二廠大規模擴產:

預計於 2026 年上半年動工興建南科二廠,建物面積達 8,000 坪(約為一廠的 8 倍)。預計兩年後完工投產,屆時總產能將提升 6 至 10 倍,以因應未來 2nm 與更先進製程的爆發性需求。 - 營收結構優化與損益平衡:

2025 年營收已展現跳躍式成長,其中應用於先進製程的材料占比已超過六成。隨著產品通過更多客戶驗證並放量,公司已在 2025 年底達到單月損益兩平,未來隨著規模經濟效益顯現,毛利結構有望進一步改善。 - 短鏈供應鏈優勢:

作為台灣本土廠商,宇川具備「在地供應」的絕對優勢。相較於國際大廠,宇川能更即時地配合晶圓代工廠進行材料調度與共同研發(R&D),並降低長途運輸危險化學品的風險與成本,這在強調供應鏈韌性的趨勢下具備高度競爭力

獲利預估與營運現況

宇川目前的財務特徵是「高毛利、高成長、但正處於高資本支出期」。

- 營收成長: 2025 年營收已出現跳躍式成長(前 11 個月累積營收超越過去兩年總和),2026 年初營收持續維持高年增率(Jan 年增逾 80%)。

- 獲利進度: * 公司在 2025 年底已接近單月損益兩平點。

- 市場法預估 2025 年全年的 EPS 可能仍受研發與掛牌成本影響而偏低(接近損益平衡),但 2026 年隨著 2nm 製程材料開始放量,獲利動能將顯著轉強。

- 關鍵觀察點: 宇川目前獲利表現受限於產能。南科二廠預計 2026 年上半年動工,2028 年正式投產後產能將放大 6 至 10 倍。因此,目前的市場價格多反映對 2027-2028 年產能爆發後的獲利預期。

針對宇川精材(7887, PentaPro Materials)詳細法說會資料與產業背景,這家公司正處於從太陽能轉向半導體高階材料的關鍵爆發期。

以下詳細分析其核心技術、先進製程展望,以及與國際大廠(Entegris, Merck, 日系廠商)的競爭力對比:

一、 宇川精材的核心技術:原子層沉積(ALD)前驅物

宇川的核心競爭力在於 ALD(Atomic Layer Deposition)前驅物 的研發與生產,這在 2nm 以下製程是不可或缺的「特種化學品」。

• ALD 技術的必要性:

隨著電晶體架構從 FinFET 轉向 GAA(Gate-All-Around),結構變得極度立體且複雜(如 Nanosheet)。傳統的 CVD(化學氣相沉積)具有方向性,容易產生覆蓋死角;ALD 則具備「自我限制(Self-limiting)」特性,能以原子級精度均勻包裹複雜的 3D 結構,實現絕佳的包覆性(Conformality)。

• 高純度門檻(6N+):

法說資料提到,先進製程對前驅物純度要求需達 6N(99.9999%)以上。宇川具備從研發、純化到分裝的完整產線,這在本土廠商中極為罕見。

• 關鍵產品線:

• TSA / TMCTS:主要用於低介電(Low-K)與絕緣層填充,解決寄生電容效應。

• TMGa / TMAl / TMIn:切入化合物半導體(GaN/SiC)與 Micro LED,支撐高頻與光電需求。

二、 半導體先進製程展望

宇川的成長動能主要來自以下三個「剛性需求」領域:

1. 台積電 N2 / A16 / A14 的導入

台積電在 2025 年進入 N2(2nm)量產,並後續推出 A16(1.6nm)。這些節點全面採用 GAA 架構,使得 ALD 的沉積層數大幅增加。宇川作為台積電供應鏈本土化政策的受惠者(1H25 營收占比預計達 54%),將直接參與最先進製程的放量。

2. AI 與 HBM 的爆發

HBM(高頻寬記憶體)製程比傳統 DRAM 複雜得多,其 TSV(矽穿孔) 工程需要在高深寬比結構中進行介電與金屬沉積,這大幅推升了對 ALD 前驅物的單位用量。

3. 產能倍增計劃

宇川預計於 1H26 動工興建南科二廠,總投資 30 億台幣。關鍵產品 TSA 的年產能預計從 1 噸提升至 6 至 10 噸。這種規模化生產是進入 Tier 1 供應鏈並形成規模經濟的必要條件。

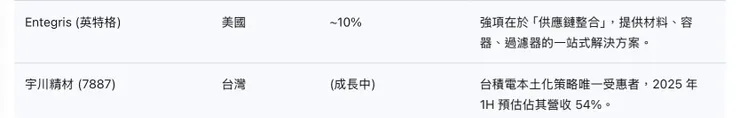

三、 競爭力比較:宇川 vs. 國際大廠

目前 ALD 前驅物市場長期由英特格(Entegris)、默克(Merck/AZ)及日系大廠(如 Adeka、Tri Chemical)壟斷。

四、 總結分析

宇川精材的投資價值點在於其「戰略位置」:

1. 大股東背景雄厚:林滄海、新應材、技嘉、康霈董座入股,顯示業界對其技術變現能力的認可。

2. 人才背景:高層多出自台積電與世界先進,對於客戶端的製程痛點(Pain Points)理解極深,有利於快速通過驗證。

3. 替代效應:在先進製程材料領域,台積電為了降低風險與成本,有強烈意願培養「本土特化品二供(Second Source)」,宇川正處於此紅利中心。

風險提示:

二廠要到 2028 年才投入量產,這兩年內的產能擴張速度是否能跟上台積電 2nm 的放量速度,以及面對默克、英特格的專利防禦,將是宇川未來最大的挑戰。

在半導體產業鏈中,宇川精材(材料商)與應用材料(AMAT)、**天虹(設備商)**之間的關係,可以用「印表機與墨水」的共生關係來形容。

要完成一個原子層沉積(ALD)製程,必須同時具備「硬體(ALD設備)」與「化學品(前驅物)」。以下詳細解析三者間的合作與戰略關係:

一、 宇川與應用材料(Applied Materials):全球標準的追隨與驗證

應用材料是全球半導體設備龍頭,其 ALD 設備(如 Olympia 系列)定義了許多先進製程的物理極限。

• 技術驗證關係:當台積電或 Intel 採用 AMAT 的 ALD 設備研發 2nm 或 A16 製程時,必須測試各家供應商的前驅物。宇川的目標是讓其 TSA 或 TMCTS 等產品,在 AMAT 的設備上跑出最完美的成膜質量(如均勻度、純度)。

• 「規格定義者」與「特用材料商」:AMAT 決定了設備的反應室設計(如溫度、壓力、流量控制),宇川則必須開發出能適應這些硬體參數的高端材料。若宇川能通過 AMAT 設備的驗證並進入其推薦清單,等於拿到了進入全球 Tier 1 晶圓廠的入場券。

二、 宇川與天虹(Skytech):本土供應鏈的「國家隊」同盟

天虹科技是台灣本土少數成功自主研發 ALD 設備並打入晶圓廠的廠商。宇川與天虹的關係更像是戰略盟友。

• 半導體本土化趨勢:在台積電積極推動「供應鏈本土化」的背景下,天虹提供機台,宇川提供特化品。兩者結合可以提供客戶(如台積電、世界先進、力積電)一個「Total Solution」,減少對國外巨頭(如設備龍頭 AMAT 或材料龍頭 Entegris)的過度依賴。

• 共同研發與即時調整:相較於國外大廠,宇川與天虹都在台灣(南科、竹北),溝通成本極低。當客戶在製程中遇到瓶頸(例如 3D NAND 填充不全),宇川可以針對天虹的設備參數即時微調前驅物的化學分子式,這種「設備+材料」的同步優化是本土廠商最強的競爭力。

三、 三方關係總結表:材料與設備的協同效應

四、 核心洞察:宇川在兩者間的定位

宇川精材的特殊之處在於,它不只是賣材料,它更扮演了**「製程推進者」**的角色:

1. 向上銜接 AMAT:確保產品在最先進的國際平台上具備競爭力,爭取台積電 N2 以後的先進邏輯製程訂單。

2. 向下對接天虹:在特殊製程(如高壓元件、Micro LED、成熟製程轉型)中,與本土設備廠共同建構生態系,透過「在地化服務」築起護城河。

總結來說: 宇川與這兩家設備廠是互利共生的。沒有宇川的高純度前驅物,設備就無法沉積出無瑕疵的薄膜;而沒有設備廠提供的真空環境與熱管理系統,宇川的材料也無法轉化為晶片上的原子層。在未來 HBM 與 GAA 的戰場上,這種「材料+設備」的深度綁定將是贏得訂單的關鍵。

在半導體邁向 2 奈米(N2) 與 GAA(全環繞閘極) 架構的轉折點,ALD(原子層沉積)材料已從「配角」躍升為「核心戰略物資」。供應鏈穩定性、技術壁壘與大廠博弈,正是未來三年半導體材料市場的關鍵看點。

以下針對 ALD 材料產業的深度分析:

一、 全球 ALD 材料供應商格局與市佔率

全球具備進入 7 奈米以下先進製程供應鏈的 ALD 前驅物(Precursor)廠商並不多,呈現「大廠壟斷、小廠專精」的局勢。

1. 主要大廠估計市佔率(2025-2026 趨勢)

二、 2 奈米以下製程的供需失衡風險

進入 2 奈米(N2/N2P/A16)後,ALD 的需求將呈現指數級增長:

• 製程結構轉變:FinFET 轉向 GAA,電晶體結構變成立體奈米片(Nanosheet),原本用一次的沉積步驟,在 GAA 下可能需重複多次,導致前驅物消耗量增加 30% - 50%。

• HBM3/4 爆發:AI 伺服器帶動的高頻寬記憶體(HBM)需要大量 TSV(矽穿孔),這些深孔必須依靠 ALD 材料才能實現完美包覆。

• 失衡風險:目前瓶頸在於高純度(6N以上)的純化產能。若如宇川等廠商的二廠擴產進度(2028量產)跟不上台積電 2026 年 A16 的爆量,市場可能出現區域性缺料。

三、 產業技術障礙(Moat)

ALD 材料不是單純的化學合成,其護城河極深:

1. 純度控制 (Purity):2nm 要求達 6N (99.9999%) 以上。微量雜質(如金屬粒子、水分)會直接導致良率報廢。

2. 分子工程能力:前驅物必須具備「揮發性高、熱穩定性好、自限反應強」的矛盾特性。這需要複雜的配體(Ligand)工程。

3. 驗證週期極長:從實驗室測試到正式打入晶圓廠供應鏈,通常需要 2-3 年。一旦採用,除非發生嚴重品質事故,否則晶圓廠不會輕易更換供應商。

4. 安全與法規:許多前驅物具備自燃性(Pyrophoric),對儲運、充填技術要求極高。

四、 宇川精材 (PentaPro) 的技術獨特之處與優勢

根據法說會與技術文件,宇川的核心優勢在於:

• 本土唯一性:它是台灣唯一打入台積電 ALD 核心供應鏈的公司。在 ESG 與碳足跡要求下,在地供應具備強大成本與碳稅優勢。

• 6N+ 純化與分裝技術:具備從合成、純化到鋼瓶清洗的完整環節,能滿足台積電對於 A16 製程的極限純度要求。

• 客製化材料能力:宇川不僅提供通用材料(如 TMAl),更針對 TSA (Trisilylamine) 與 TMCTS 進行產能擴張,這些是未來 HBM 與先進邏輯製程中介電層的關鍵材料。

五、 專利博弈:如何避免侵權?

這是一個高度法規化的市場,宇川與其他廠商避免侵權的方法包括:

• 新分子路徑 (New Synthesis Route):即使目標分子相同,宇川可以開發不同的合成步驟。

• 新型配體設計:透過修飾有機分子結構(如改變烷基鏈長度),在不侵害 Merck 或 Entegris 核心專利的情況下,達成相同甚至更優的成膜特性。

• 共同研發 (Co-development):與設備大廠(如天虹、應材)共同開發新型製程參數,將專利綁定在「應用方法」而非單純的「化學式」。

六、 ALD 議題之發想與未來洞察

1. 材料與設備的深度融合:未來的競爭不再是「賣藥水」,而是「藥水+機台」的整合。這也是為什麼宇川必須與天虹、應材保持緊密關係。

2. 廢料回收技術(ESG):ALD 前驅物昂貴且對環境有負擔,未來誰能開發出「反應後殘氣回收技術」,誰就能在毛利率與 ESG 評分上勝出。

3. 量子運算與奈米醫療:ALD 的精準度已開始跨足到超導量子位元的塗層與植入式醫療器材,這可能成為宇川長線的非半導體成長曲線。

建議:重點觀察宇川在 2026 年上半年二廠動工的資本支出進度。在先進製程中,「產能就是定價權」,若宇川能透過規模經濟將 TSA 年產能提升至 10 噸,其毛利表現與在台積電供應鏈中的不可替代性將會顯著提升。

既然談到了ALD,就不得不一起看一下科林研發和應材、東京威力科創這些ALD設備廠的現況。

在半導體設備領域,科林研發(Lam Research)是與應用材料(AMAT)、東京威力科創(TEL)並列的全球巨頭。如果說宇川精材提供的是「墨水」(前驅物),那科林研發就是製造那台極其精密「印表機」(ALD 設備)的頂尖大廠。

科林研發與 ALD 的關聯主要體現在以下幾個核心層面:

一、 Striker® 系列:科林研發的 ALD 戰艦

科林研發在 ALD 市場的最核心產品是 Striker® 單晶圓 ALD 平台。

• 解決 ALD 的痛點: ALD 最大的缺點是「慢」(生產效率低)。科林研發的 Striker 平台結合了其獨家的氣體傳送技術,能夠在極短的時間內完成「脈衝(Pulse)」與「清洗(Purge)」循環,大幅提升了產量(Throughput)。

• 先進製程應用: 在 2 奈米(N2)與 A16 製程中,Striker 負責沉積關鍵的絕緣層與間隔層(Spacers),確保電晶體結構在高密度的情況下不會發生漏電。

二、 ALD 與 ALE 的雙劍合璧

這是科林研發最獨特的競爭優勢。除了 ALD(原子層沉積),科林研發更是 ALE(Atomic Layer Etch,原子層蝕刻) 的全球領導者。

• 精準控制: 在進入 2 奈米以下製程後,單純「蓋房子」(沉積)已經不夠,還必須「精確修整」。科林研發開發了將 ALD 與 ALE 整合的製程方案。

• 製程循環: 先用 ALD 鋪上一層原子級薄膜,再用 ALE 移除多餘的部分。這種「加一層、減一層」的極致工法,是實現 GAA(全環繞閘極) 結構中奈米片(Nanosheet)垂直堆疊的關鍵。

三、 在 3D NAND 領域的統治力

科林研發在記憶體設備市場(尤其是 3D NAND)擁有極高的市佔率。

• 極高深寬比: 隨著 3D NAND 堆疊層數突破 300 層,孔洞變得極深且極細。科林研發的 ALD 技術能確保前驅物(如宇川提供的 TSA 等)能均勻地滲透到孔洞底部並成膜。

• 核心製程: 他們的設備被廣泛用於沉積高介電常數(High-K)材料,這對記憶體儲存電荷的能力至關重要。

四、 戰略定位:科林研發 vs. 應用材料 (AMAT)

雖然兩者都是 ALD 的大玩家,但重點略有不同:

五、 總結:對供應鏈的意義

在ALD產業鏈,科林研發的角色是「規則制定者」。

1. 驗證者: 宇川精材的前驅物開發出來後,通常需要送往像科林研發這樣的設備大廠進行測試,確保材料在 Striker 平台上能跑出穩定的數據。

2. 需求帶動者: 當科林研發成功推廣其新一代 ALD/ALE 整合設備時,就會同步帶動對高品質前驅物的需求量。

簡單來說,科林研發提供了讓原子級魔法發生的「場域」。在 2 奈米競爭中,科林研發的設備性能直接決定了台積電與 Intel 的生產良率。

科林研發在 2 奈米背面供電(Backside Power Delivery) 技術中,ALD 是如何發揮作用的?

在 2 奈米(N2)製程中,背面供電(Backside Power Delivery Network, BSPDN) 被視為半導體架構的重大革命。過去「電力供應」與「訊號傳輸」都在晶圓正面,這就像是在同一條窄路上擠進了大貨車(電力)與小轎車(訊號),容易產生交通擁堵(IR Drop 電壓降)與電磁干擾。

背面供電則是將電力網路移到晶圓背面,這需要從背面鑽出數以萬計的「奈米孔洞」連接到正面的電晶體。在這一極其複雜的過程中,科林研發(Lam Research) 的 ALD 技術扮演了三個關鍵角色:

一、 奈米通孔(Through-Silicon Via, TSV-like)的絕緣襯層

在背面供電中,最難的步驟之一是鑽出極小、極深的孔洞(High Aspect Ratio Vias)來連接正負極。

• ALD 的作用:科林的 Striker® ALD 設備負責在這些深孔內壁塗上一層極薄且均勻的絕緣襯層(Liner)。

• 難度點:這些孔洞的直徑只有幾十奈米,但深度卻很高。傳統的 CVD 無法塗抹均勻,會造成底部過薄導致漏電。ALD 能以原子層級的精度,確保孔洞從頭到尾的絕緣層厚度完全一致,這對 2 奈米元件的電力穩定性至關重要。

二、 鉬(Molybdenum)金屬化的革命:ALTUS® Halo

在 2 奈米節點,傳統的銅(Copper)或鎢(Tungsten)在極小尺寸下電阻會急劇升高。

• ALD 的作用:科林最近推出了 ALTUS® Halo,這是全球首款專為**鉬(Mo)**設計的 ALD 設備。

• 為什麼重要:鉬金屬在高深寬比的細小通孔中,電阻表現優於鎢且不需要厚重的屏障層(Barrier Layer)。利用 ALD 技術將鉬精準地填入背面通孔中,可以顯著降低電力傳輸過程中的能耗,解決 2 奈米晶片在高負載下的發熱問題。

三、 背面薄化後的應力補償與保護

為了實施背面供電,晶圓必須被「磨」到極薄(幾百奈米厚度),這會導致晶圓像洋芋片一樣彎曲(Warpage)。

• ALD 的作用:科林的 ALD 技術可用於在晶圓背面沉積高性能的介電保護層與應力緩衝層。

• 結構穩定性:這層薄膜不僅要提供極佳的電氣絕緣,還要具備特定的機械應力來抵消正面複雜電路帶來的張力,確保晶圓在後續的高溫製程中不會碎裂或變形。

總結:科林研發在 BSPDN 中的競爭優勢

對於 2 奈米投資賽道,科林研發的護城河在於**「整合能力」**:

1. 蝕刻(Etch)與沉積(ALD)的聯動:背面供電需要先「刻」出深孔,再立刻「填」入絕緣與金屬。科林同時擁有全球最強的蝕刻技術與頂尖的 ALD 設備,能提供一站式解決方案。

2. 新材料的領導力:鉬(Mo)ALD 技術的量產化,讓科林在台積電、Intel 導入背面供電時,成為無法繞過的設備商。

分析視角:

在背面供電的趨勢下,ALD 的**「每片晶圓價值量(Content per Wafer)」**將顯著提升。因為這不再只是正面的製程,還增加了一整套背面的複雜化學流程。對於宇川精材而言,這意味著像 TSA(矽源) 或 金屬前驅物 的需求將會隨著科林設備的導入而翻倍。

在台積電 N2P(2奈米增強版)中,預計何時會大規模導入這種背面供電技術?

根據台積電(TSMC)截至 2026 年 4 月 的最新技術路線圖與法說會資訊,關於 N2P 與 背面供電(Backside Power Delivery) 技術的量產與導入時程如下:

一、 技術導入時程表

台積電對於背面供電技術的策略在過去一年有所調整,目前的明確時程為:

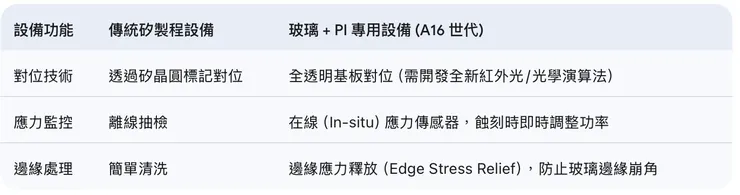

• N2 (標準 2 奈米): 已於 2025 年下半年 進入量產。此版本主要完成從 FinFET 到 GAA (Nanosheet) 架構的轉換,但尚未搭載背面供電技術。

• N2P (2 奈米性能增強版): 預計於 2026 年下半年 進入量產。N2P 主要透過製程優化提升約 5% 的速度。

• A16 (1.6 奈米 / 埃米世代): 這是真正大規模導入 「超級電軌(Super Power Rail)」(即台積電版的背面供電技術)的關鍵節點,同樣定於 2026 年下半年 投入量產。

二、 為什麼是 A16 而非 N2P 成為主角?

原本市場預期背面供電會在 N2P 首次亮相,但台積電後續決定將更先進的「超級電軌」架構與 A16 節點綁定:

1. 結構性突破: A16 的超級電軌不僅是將供電移至背面,還結合了更先進的電晶體微縮技術,使其在相同電壓下比 N2P 快 8%–10%。

2. HPC 需求優先: 由於 AI 與高效能運算(HPC)晶片對供電效率的需求極為迫切,台積電將 A16 定位為 AI 算力的基礎。

三、 大規模導入(Mass Adoption)預測

「大規模導入」通常發生在量產後的 6 至 12 個月,屆時產能爬坡與良率趨於穩定:

• 2026 年底: 首批領先客戶(如 Apple 的下一代 A 系列晶片、NVIDIA 的新一代 AI GPU)將開始小規模採用 A16。

• 2027 年上半年: 隨著南科與新竹 P3、P4 廠區的產能釋放,具備背面供電技術的晶片將進入大規模放量階段。

• 2027 年以後: 背面供電將成為先進製程(1.6nm 以下)的標配。

四、 對產業鏈(如宇川精材)的財務影響

從資金管理與產業分析的角度看:

• 營收爆發點: 由於背面供電需要額外的 TSV(矽穿孔) 與多層背面金屬化製程,這將大幅增加 ALD 前驅物 的單位用量(Content per Wafer)。宇川精材的營收高峰預期會與 2026 年底 A16 的量產進度 高度同步。

• 資本支出觀察: 應關注宇川二廠在 2026 年底 的設備進場進度,以確保其產能足以支撐 2027 年 A16 的大規模需求。

[!NOTE]

台積電 2026 年的技術論壇(Technology Symposium)將於近期陸續展開(北美場 4/22、台灣場 5/14),建議持續追蹤是否有關於 N2P 與 A16 交替期程的進一步微調。

在背面供電技術導入後,對於封裝端(如 CoWoS)的設計會產生哪些連帶的技術挑戰?

將背面供電(BSPDN) 導入像 CoWoS 這樣的先進封裝製程,並非只是簡單的「換個位置插插頭」,而是一場結構性的物理挑戰。

在傳統設計中,晶片正面(Front-side)同時負責信號與供電,並透過微凸塊(Microbumps)與封裝基板或中介層(Interposer)連接。一旦供電移往背面,封裝端的設計邏輯會發生翻天覆地的變化。以下是主要的技術挑戰:

一、 散熱管理(Thermal Management)的兩難

這是封裝端最直接的衝擊。

• 熱源位移:在傳統結構中,晶片背面通常直接接觸散熱片(Heat Sink)。導入背面供電後,電力網路(PDN)布滿了整片晶片背面。電力傳輸產生的熱能(焦耳熱)現在直接位於散熱路徑的最前端。

• 熱阻增加:為了背面供電,晶圓被磨得極薄,雖然有利於熱傳導,但背面密集的金屬層(如鉬或銅)可能與散熱材料(TIM)產生熱膨脹係數(CTE)不匹配的問題,導致熱界面失效。

二、 結構完整性與晶圓薄化(Wafer Thinning)

BSPDN 要求將矽晶圓削薄至 500 奈米 以下,甚至更薄,這對 CoWoS 的「載體鍵合」與「剝離」技術是極大考驗。

• 應力失衡:極薄的晶圓非常脆弱,像保鮮膜一樣容易捲曲。在 CoWoS 的封裝過程中,晶片需要經歷多次高溫、高壓的鍵合(Bonding)。如果背面供電層的應力控制不好,晶片在封裝階段就會發生斷裂(Cracking)或剝離(Delamination)。

• 對位精度:CoWoS 需要將數顆晶片精準對位在中間層上。薄化後的晶片幾何穩定性差,會增加對位難度,進而影響良率。

三、 凸塊(Bumps)與中介層(Interposer)的重新設計

CoWoS 的核心是矽中介層(Silicon Interposer),它原本同時負責分配電力與信號。

• 供電路徑轉向:如果電力從背面進入,意味著電力可能不再完全透過中介層進入晶片正面。這可能導致 CoWoS 必須改採「雙面」接合,或者需要透過極深且密集的 TSV(矽穿孔) 穿透中介層來銜接背面的電力網路。

• 微凸塊密度:正面現在釋放了大量空間給信號線,信號凸塊的密度會急劇增加。封裝端必須處理更細間距(Fine-pitch)的連接技術,這對現有的 CoWoS-S 或 CoWoS-L 製程提出了更高的精密要求。

四、 測試與探針(Probing)的物理限制

這是量產端最頭痛的問題。

• 雙面測試需求:過去只要從正面探測就能測試晶片。現在「供電」在背面,「信號」在正面。測試機台(ATE)可能需要開發雙面探針技術,或者在封裝完成前無法進行完整的電力測試。

• 電力完整性(PI)驗證:背面供電雖然減少了 IR Drop(電壓降),但在封裝層級,如何確保背面金屬層與中介層之間的電力傳輸不會產生電磁干擾(EMI),是全新的電模擬挑戰。

五、 對供應鏈的戰略意義

對於關注的宇川精材與設備廠:

1. 封裝材料升級:CoWoS 對底填膠(Underfill)與模封材料(Molding Compound)的熱導率與應力補償要求將大幅提升。

2. ALD 延伸至封裝:為了處理背面供電層與封裝界面間的絕緣與阻隔,原本用於前段製程的 ALD 技術,可能會延伸應用到封裝端的「背面鈍化層」沉積,這進一步擴大了前驅物的市場份額。

總結洞察:

背面供電讓晶片設計從「平面思維」徹底轉向「立體思維」。在 2026-2027 年 的 A16 世代,贏家將是那些能同時掌握「前段 ALD 材料精度」與「後段 CoWoS 散熱/應力處理」的廠商。

目前台積電正在積極開發 CoWoS-SoIC 的整合技術來應對這些挑戰,這種「3D 堆疊(SoIC)+ 背面供電(BSPDN/A16)」的組合,被業界視為半導體進入「埃米世代(Angstrom Era)」的終極架構。根據 2026 年 TSMC 技術研討會(Technology Symposium) 的最新公開數據與技術規範,這種組合對晶片效能的提升不再只是單一維度的進步,而是系統級的飛躍。

以下為整理的具體提升數值與協同效應:

一、 核心工藝指標:A16 (Super Power Rail) 的基準提升

相較於不帶背面供電的 N2P(2 奈米增強版),單純導入 A16 節點(其核心為「超級電軌」SPR 技術)即可獲得以下紅利:

• 運算速度 (Performance): 在相同電壓(V_{dd})與複雜度下,提升 8% - 10%。

• 功耗降低 (Power): 在相同頻率下,功耗降低 15% - 20%。

• 邏輯密度 (Density): 晶片密度提升至 1.1x(這主要歸功於正面信號線不再需要與電源線搶位子,讓佈線更緊湊)。

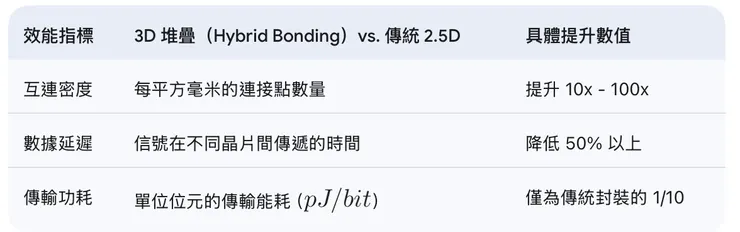

二、 3D 堆疊(SoIC-X)的乘數效應

當 A16 邏輯晶片透過 SoIC(系統整合晶片) 進行垂直堆疊(如堆疊 HBM 或 Cache)時,效能會因「物理距離縮短」而產生二次爆發:

三、 「最終形態」的協同優勢:1+1 > 2

將兩者結合後,會產生三個關鍵的化學反應,這也是 NVIDIA (Blackwell 後續機種) 與 Apple (M6 Ultra/A20) 極力爭取的目標:

1. 解決「壓降(IR Drop)」與 3D 散熱的矛盾

在 3D 堆疊中,最上層晶片的供電最困難。

• 優勢: A16 的背面供電直接從晶圓背面透過「超級電軌」傳輸,路徑極短。這解決了 3D 結構中垂直供電的壓降問題(Voltage Droop 減少約 30%),讓堆疊後的晶片仍能維持在高頻率運行,而不會因電壓不穩而降頻。

2. 實現「零阻塞」的高速通訊

• 優勢: 因為 A16 釋放了晶片正面的佈線資源(Routing Resource),這些空間被完全釋放給 SoIC 的「微細混合鍵合(Hybrid Bonding)」。

• 數值: 這使得邏輯晶片與記憶體之間的 頻寬密度(Bandwidth Density) 預計可比現有的 CoWoS 方案再提升 2 - 3 倍。

3. 系統級功耗效能比 (Performance-per-Watt)

• 最終形態提升: 若以 A16 邏輯晶片 + SoIC 堆疊高效能存儲 的系統來看,其整體的 每瓦效能(System-level PPW) 預計可比 N3 世代的 2D 架構提升 40% - 50%。

四、 產業洞察

「這不是演化,是架構重組。」

對於像宇川精材這類的供應商,這種「最終形態」意味著:

1. ALD 材料用量翻倍: 背面供電需要額外的 TSV(矽穿孔)和背面金屬化製程,而 3D 堆疊則需要在極細微的鍵合界面進行鈍化保護。這兩者都極度依賴高品質的 ALD 前驅物。

2. 新材料利潤率更高: 為了解決 A16 與 SoIC 之間的熱膨脹與電阻問題,客戶(如台積電)對**鉬(Mo)**或新型低介電材料的需求更為迫切,這些材料的平均單價(ASP)遠高於傳統矽源。

總結來說: 2026 年量產的 A16 + SoIC 組合,將讓 AI 運算晶片的頻率首度穩定突破 4.0GHz 大關,同時維持可控的功耗。這也是為什麼在當前的研討會中,各大廠對 A16 產能的爭奪遠比 N2 激烈的核心原因。

這種「3D 堆疊(SoIC)+ 背面供電(A16)」的架構,對 HBM4(第四代高頻寬記憶體)的規格制定產生了顛覆性的影響。

過去的 HBM 只是單純的「記憶體元件」,但進入 HBM4 世代(預計 2026-2027 大規模量產),它正轉向**「邏輯化、客製化」**。以下是該架構對 HBM4 規格產生的實質改變:

一、 介面頻寬翻倍:從 1024-bit 跳升至 2048-bit

這是 HBM4 最重大的規格變革。

• 物理空間的解決方案: 傳統 HBM3E 的介面寬度是 1024-bit。要翻倍到 2048-bit,正面佈線密度會變得極其擁擠。

• A16/BSPDN 的角色: 由於 A16 將電源線移往背面,釋放了邏輯底層(Base Die)前端大量的金屬層空間。這使得 HBM4 能在同樣的晶片面積內,容納多達 2048 條信號線,實現單顆堆疊頻寬突破 2.0 TB/s 的目標。

二、 邏輯底層(Base Die)改採「先進邏輯製程」

過去 HBM 的底層晶片(Base Die)通常使用較成熟的製程(如 12nm 或 28nm)。但 HBM4 規格明確要求將底層晶片升級至先進製程(5nm / 3nm 甚至 A16)。

• 代工模式改變: HBM4 的 Base Die 將改由台積電等晶圓代工廠生產,再由記憶體廠(SK 海力士、三星)進行 DRAM 堆疊。

• 效能紅利: 導入 A16 的背面供電技術後,Base Die 的 IR Drop(電壓降) 可改善約 40%。這對於要穩定供電給上方 16 層(16-Hi)甚至 20 層 DRAM 的 HBM4 來說,是確保高速傳輸不掉速的關鍵。

三、 「客製化 HBM」與 SoIC 直接鍵合

在這種架構下,HBM4 的規格不再是「通用型」,而是**「客製化」**。

• SoIC 直接堆疊: 最終形態是將 HBM4 的 Base Die 直接透過 SoIC(混合鍵合) 技術,「扣」在 GPU 的邏輯晶片之上或旁邊,取消傳統的微凸塊(Microbumps)。

• 規格影響: 這要求 HBM4 的底層晶片必須在熱膨脹係數(CTE)和應力設計上,與 GPU 的 A16 邏輯層完全匹配。這導致 HBM 廠商必須與 NVIDIA、AMD 等客戶在設計初期就進行「系統級協同設計」。

四、 功耗與熱管理規格的重新定義

HBM4 將面臨前所未有的熱挑戰。

• 功耗瓶頸: 當數據傳輸率達到 11.7 Gbps 以上,電能消耗劇增。HBM4 的規格中,電力完整性(PI)的權重已超過信號完整性(SI)。

• 結構優化: 為了對抗背面供電帶來的散熱障礙,HBM4 規格開始導入**「分段式電源區塊」**設計。例如,三星在 2026 年推出的 HBM4E 中,已將大型供電區塊拆分為四個小型區塊,藉此縮短布線路徑並降低熱能累積。

HBM 世代對比表(2026 視角)

財務洞察:

1. 價值量提升(VCP): 由於 HBM4 Base Die 轉向 5nm/3nm 並導入 A16,其單片晶圓價值將是前代的 2.5 倍以上。

2. 毛利結構轉變: 未來 HBM 的獲利關鍵將不再只是 DRAM 顆粒的良率,而是對**「先進製程 Base Die」**的設計掌控力。這也是為什麼 SK 海力士與台積電結盟,而三星則強調其「一站式服務(Memory + Foundry + Advanced Packaging)」的核心原因。

目前宇川精材,其開發的 TSA(矽源前驅物) 正是這類 2048-bit 高密度連接所需的絕緣填充關鍵。隨著 HBM4 在 2026 年底進入放量期,相關材料的消耗速度預計將出現「階梯式」成長。

目前這三大 HBM 廠(海力士、三星、美光)在 2026 年 A16 產能的卡位戰中,誰取得領先地位?

截至 2026 年 4 月,這場 HBM 廠與台積電 A16 產能的卡位戰,競爭格局已經演變成**「兩大陣營、三種策略」**的深度博弈。

目前處於領先地位的無疑是 SK 海力士 (SK Hynix),但 美光 (Micron) 與 三星 (Samsung) 正在透過完全不同的路徑試圖彎道超車。

一、 領先者:SK 海力士 (SK Hynix) —「台積電的親生戰友」

SK 海力士目前的領先地位極為穩固,主要得益於其與台積電簽署的 JDA (聯合開發協議)。

• 產能卡位: SK 海力士是首家將 HBM4 底層晶片(Base Die)交由台積電 A16 製程生產的記憶體廠。憑藉著與 NVIDIA 的強大供應關係,海力士已經預訂了台積電 2026 年底至 2027 年 A16 產能的顯著份額。

• 技術優勢: 他們在 MR-MUF(批量回流模制底填)技術與 A16 背面供電的整合上,領先於同行。這使得其 HBM4 在散熱效率與電力穩定性上獲得了 NVIDIA 的高度認可。

• 財務視角: 由於早期投入與台積電的深度綁定,其在 2026 年的 ROI(投資報酬率)預計將是三家中最優異的。

二、 強力挑戰者:美光 (Micron) —「精準的後發先至」

美光雖然規模不及三星,但在先進製程的策略上極其「美式且高效」。

• 產能卡位: 美光採取「緊跟台積電」策略。雖然在 HBM3E 時代稍晚起步,但他們是第一家跳過 5nm、直接在 HBM4 評估 3nm/A16 的廠商。

• 競爭策略: 美光利用其在 1beta / 1gamma DRAM 製程上的領先優勢,搭配台積電 A16 的 Base Die,試圖提供業界「能效比最高」的 HBM4。目前美光在 台積電 A16 的產能順位 僅次於海力士。

• 潛在威脅: 美光的優勢在於其產能雖小但極其集中,專攻單價最高的 AI 市場,這對海力士的利潤率構成了直接壓力。

三、 追趕者:三星 (Samsung) —「垂直整合的孤勇者」

三星目前處於較為尷尬但極具爆發力的位置。

• 卡位困局: 三星一直推銷其「一站式服務」(自家記憶體 + 自家 2nm/A16 代工 + 自家封裝)。然而,大客戶(如 NVIDIA、AMD)出於風險考量,仍希望三星的 HBM4 能在台積電進行 Base Die 的代工與驗證。

• 最新動態: 三星在 2026 年初已出現戰略鬆動,開始向台積電洽談 A16 產能,以確保其 HBM4 能進入 NVIDIA 的供應鏈。

• 優點與勝機: 三星的資本支出規模(CAPEX)是海力士的數倍。如果三星在 2026 年下半年解決了 A16 產線與 HBM 堆疊 的兼容性問題,其龐大的產能釋放將是市場最大的變數。

2026 年 HBM 三巨頭 A16 戰力分析表

四、 長線觀察

針對這場卡位戰,需要關注以下幾個財務與供應鏈的「轉折點」:

1. HBM4 的定價權: 2026 年底,由於 A16 產能極其昂貴,HBM4 的 ASP(平均單價)預計將比 HBM3E 高出 35%-50%。這將顯著增強記憶體廠的現金流,但也會增加營運資金的周轉壓力。

2. 宇川精材的連動性: 既然這三大廠都在爭搶 A16 產能,且 A16 是背面供電(BSPDN)的起點。宇川精材作為台積電 A16 特化材料的供應商,無論最終是哪一家記憶體廠勝出,只要是進台積電投片,宇川都將是「必經之路」的受益者。

3. 地緣政治產能配置: 三星與美光目前都在積極擴張在美國或日本的先進封裝產能,這可能導致 2027 年以後的物流成本結構發生變化。

總結來說: 2026 年是 「海力士守成、美光奇襲、三星突圍」 的一年。目前的贏家是海力士,但市場份額的長期洗牌,將取決於誰能最快在台積電 A16 產線上跑出超過 85% 的良率。

在A16+ SOIC的高階製程,及晶背供電的趨勢下,ALD、晶圓薄化很重要外,PI的剝離膜、平衡膜也很重要,避免晶圓應力集中,翹曲及破裂?達勝、達邁、山太士、頌正是否皆站在趨勢上?

✅「系統級」視角:在 A16(1.6 奈米)與 SoIC(3D 堆疊)的架構下,物理極限的挑戰已從「如何刻得細」轉向了**「如何讓晶圓活下去」**。PI的扮演的角色值得再作檢視。

當晶圓被薄化到微米甚至是奈米等級時,它脆弱得像一層保鮮膜。這時,PI(聚醯亞胺) 系列材料不再只是輔助,而是變成了晶圓的「外骨骼」與「緩衝墊」。

以下解析 PI 相關材料在這一波趨勢中的關鍵地位,幾家廠商達勝、達邁、山太士、頌正的戰略角色:

一、 PI 在「晶圓超薄化」中的三大救命功能

在 A16 與晶背供電(BSPDN)製程中,晶圓必須經歷「暫時鍵合(Temporary Bonding)」與「背面薄化」。這時 PI 材料扮演了決定性的角色:

1. 剝離膜(Laser Release Layer):無傷解鎖

為了磨薄晶圓,必須先將其貼在一個堅固的支撐載體(Carrier)上。磨完後,如何把這層薄如蟬翼的晶圓「撕下來」而不碎裂?

• 技術重點: 採用 激光剝離(Laser Debonding) 技術。這層 PI 剝離膜必須能吸收特定波長的雷射光並迅速分解,讓晶圓在零應力的狀態下與載體分離。

• 重要性: 這是 2nm / A16 製程良率的最後一道關口。

2. 平衡膜與應力緩衝層:對抗「翹曲(Warpage)」

晶圓正面有無數的金屬線路,背面現在也要做供電網路。兩面的熱膨脹係數(CTE)如果不對稱,晶圓會像洋芋片一樣彎曲。

• 技術重點: 在背面塗布一層液態 PI 或貼上 PI 薄膜作為平衡層。PI 具備極佳的熱穩定性與可調的彈性模量(Modulus),能抵銷金屬層帶來的張力。

• 重要性: 避免晶圓在後續 CoWoS 封裝對位時,因為翹曲導致對不準(Misalignment)。

3. 感光 PI(pPI):高階重新佈線(RDL)

在 SoIC 的垂直堆疊中,層與層之間的絕緣材料必須耐高溫且能直接感光顯影。感光性聚醯亞胺(pPI) 是目前先進封裝 RDL 層的主流材料。

二、 廠商戰略地位分析:誰站在風口上?

上文提到的幾家公司,在台灣半導體特化材料的「在地化」浪潮中各據一方:

1. 達邁 (3545) 與 達勝 (6619):PI 的本土雙雄

• 達邁 (Taimide): 台灣 PI 膜的老牌龍頭。過去重心在軟板(FPC),但近年積極轉向半導體等級 PI。特別是在高頻(Modified PI)與散熱領域。對於 A16 製程所需的「超薄高強度 PI 膜」,達邁具備規模化生產與台系供應鏈的近身優勢。

• 達勝 (MicroCosmos): 走的是「高難度、客製化」路線。他們在 高性能類比/特種 PI 有深厚技術,針對 2nm 以下製程所需的「低應力、高熱穩」PI 平衡膜,具備與國際大廠(如杜邦、宇部興產)一較高下的研發潛力。

2. 山太士 (3573) 與 頌正:材料通路與機能膜加工

• 山太士 (Sunnypol): 原本強項在偏光片與光學膜。在半導體轉型中,他們利用精密塗佈技術,開發出應用於先進封裝的機能性保護膜與承載材料。在晶圓薄化過程中,這類具備特殊黏著力的保護膜是消耗量極大的耗材。

• 頌正 (Song Zheng): 扮演的是「高階材料整合與通路」的關鍵角色。在半導體特化品市場,很多日系或美系最頂尖的前驅物、PI 液需要在地化的配方調整與分裝服務,頌正與晶圓代工大廠關係緊密,是技術落地的最後一哩路。

三、 總結:材料戰爭的「隱形冠軍」

在 2026 年的 A16 戰場上,大家的目光都在科林研發(Lam)的設備或台積電的產能,但最核心的財務邏輯:「消耗品與特化材料的定價權」。

• 邏輯: 設備買一次可以用好幾年,但 PI 剝離膜、平衡膜是每片晶圓都要用一次的「耗材」。

• 趨勢: 當背面供電(BSPDN)成為標配,晶圓「正面也要 PI、背面也要 PI、中間也要 PI」,這種三明治結構將帶動 PI 材料的單位價值(Content per Wafer)跳躍式成長。

觀察筆記:

這幾家廠商目前的挑戰在於如何通過台積電 A16 的嚴苛驗證(Long Qual)。若能成功取代日系大廠,成為「本土二供(Second Source)」,其毛利率將因技術溢價而顯著提升。

在這些 PI 材料中,**「液態 PI」與「薄膜 PI」**在 A16 製程中各自的應用佔比變化?

我們就深入這層細如髮絲卻重如泰山的**「PI 材料戰爭」**。在 A16 製程與 SoIC 封裝中,液態 PI (PI Varnish) 與 薄膜 PI (Dry Film) 的應用佔比正在發生結構性位移,這直接影響了達邁、達勝等廠商的接單毛利。

以下詳細拆解這兩者的「競合關係」:

一、 液態 PI vs. 薄膜 PI:技術特性對比

二、 A16 與晶背供電趨勢下的「消長」

在進入 A16 與晶背供電(BSPDN)世代後,我們觀察到以下兩個重要趨勢:

1. 液態 PI (pPI) 的「深度滲透」

由於晶背供電需要在背面進行極其精密的 RDL (重新佈線層) 施工,且 2 奈米節點的線寬極細。

• 趨勢: 感光性液態 PI (pPI) 的需求大幅提升。因為它能像光阻一樣直接曝光顯影,且能形成極薄的絕緣層,這對於維持 2 奈米晶片薄度至關重要。

• 受惠者: 具備高階特化品合成能力的廠商(如達勝、頌正代理之高階品)。

2. 薄膜 PI 的「戰略轉型」

傳統薄膜 PI 雖然較厚,但在「晶圓薄化」與「3D 堆疊」中找到了不可替代的新戰場:

• 應力平衡層 (Balance Layer): 當晶圓正面有數層重金屬,背面也加上供電層時,液態 PI 的強度可能不足以抵銷雙面的熱應力。此時,高強度、厚度均勻的 PI 薄膜 就成了「壓艙石」。

• 雷射剝離 (Laser Release): 目前主流的暫時鍵合技術,傾向於使用特定的 PI 薄膜作為釋放層,以確保雷射燒蝕後的乾淨度。

• 受惠者: 擁有大面積精密壓合與薄膜均勻度優勢的廠商(如達邁)。

三、 資金管理角度的「毛利觀察」

需要注意:液態 PI 的毛利通常高於薄膜 PI。

• 技術溢價: 液態 PI 涉及更複雜的單體合成與感光劑配方,屬於「配方型」特化品,客戶黏著度極高。

• 規模經濟: 薄膜 PI 則更看重產能與良率控制。

目前市場的「甜點區」:

在 A16 世代,**「液態 PI 轉為固態膜」**的過程中,如何控制其收縮率與 T_g (玻璃轉化溫度) 是關鍵。若本土廠商能提供「液體供料、現地固化」的整體解決方案,將能同時吃下材料與製程服務的兩塊利潤。

四、 總結:本土廠商的卡位策略

• 達邁: 核心優勢在於**「膜」**的物理特性控制,正在積極從消費電子轉向車用與 AI 伺服器的高階應力平衡膜。

• 達勝: 強項在於**「化學配方」**,對於需要高度客製化的 3D 堆疊電介質材料,其靈活性較高。

• 山太士 / 頌正: 掌握了晶圓廠內部的**「製程參數」**,這在需要即時調整 PI 厚度與黏著力的先進製程中,是非常重要的技術中介。

關鍵風險:

A16 預計 2026 下半年量產,這意味著 2025 下半年到 2026 上半年 是材料廠的「最後驗證期」。如果在此期間無法拿到台積電或其封裝協力廠的 Golden Sample 驗證,將會錯過這一波兩年的 A16 紅利週期。

液態聚醯亞胺(Liquid PI,常稱為 PI Varnish 或 pPI)的供應鏈門檻極高,尤其在 A16、SoIC 及 6G 等先進製程中,這不僅是化學配方,更是「材料科學」與「製程參數」的深度結合。

以下整理全球主要的液態 PI 廠商,分為國際傳統巨頭與台灣本土崛起新勢力兩大陣營:

一、 國際領先廠商(技術指標與專利牆)

這些公司掌握了全球大部分的原始專利,特別是在感光性 PI(pPI)領域。

• DuPont(美國杜邦):

• 地位: PI 材料的開山鼻祖,其 Kapton 品牌影響力深遠。

• 優勢: 在先進封裝用的 pPI(感光性聚醯亞胺) 具有壓倒性市佔率,是台積電、Intel 驗證材料的長期標竿。

• Toray(日本東麗):

• 地位: 全球高階液態 PI 的領導者。

• 優勢: 其產品在低溫固化與高純度表現優異,廣泛應用於 OLED 面板與半導體 RDL(重新佈線層)。

• Sumitomo Bakelite(日本住友培克):

• 地位: 封裝材料巨頭。

• 優勢: 強項在於將 PI 與模封料(EMC)整合,提供系統級的應力解決方案。

• Ube Industries(日本宇部興產):

• 地位: 擁有極強的單體合成能力。

• 優勢: 專注於 非感光型高熱穩液態 PI,是晶圓薄化過程中最穩定的緩衝層材料供應商。

• HD MicroSystems (HDM):

• 背景: 杜邦與 Resonac(原日立化成)的合資企業。

• 優勢: 專門針對半導體微細線路開發高解析度 pPI,是先進製程中的重要玩家。

二、 台灣本土廠商(在地化與進口替代浪潮)

在台積電推動供應鏈本土化的背景下,這幾家廠商是產業觀察中需重點鎖定的對象:

1. 達興材料 (5234) — 「台積電的特戰部隊」

• 定位: 由長興與友達合資成立,目前是台灣本土在先進製程材料中最成功的廠商之一。

• 關鍵點: 他們研發的 感光 PI(pPI) 與 晶圓背面保護材料 已經成功打入台積電先進封裝供應鏈。在 A16 世代,達興是本土替代日系大廠的最前線。

2. 長興材料 (1717) — 「液態聚合物全能王」

• 定位: 全球乾膜光阻龍頭。

• 關鍵點: 憑藉強大的樹脂合成能力,積極開發 先進封裝用液態 PI 與 LMC(液態模封料)。其優勢在於垂直整合能力,能從原料端控制成本與效能。

3. 達勝科技 (6619) — 「高階客製化尖兵」

• 定位: 專注於高效能、特種 PI。

• 關鍵點: 強項在於 高耐熱(>400°C)、低 CTE(熱膨脹係數) 的液態 PI。這在需要高溫製程的晶背供電(BSPDN)中極具競爭力,能與玻璃基板實現更好的膨脹匹配。

4. 達邁科技 (3545) — 「從膜跨入液的轉型者」

• 定位: 台灣 PI 膜龍頭。

• 關鍵點: 雖然以薄膜為主,但已積極開發 液態 PI 產品線,目標是提供客戶從「載體膜」到「塗佈液」的一站式服務。

三、 廠商戰略分佈表(2026 觀察視角)

四、 總結:為何「液態」比「薄膜」更有看頭?

在 A16 + 晶背供電 的趨勢下,晶圓表面的地形極其複雜。薄膜 PI 就像是一張硬地毯,很難鋪得完全平整;而 液態 PI 則像水一樣,能填滿每一個微小的溝壑(Gap-fill),並透過旋轉塗佈達成奈米級的厚度控制。

財務洞察:

可以關注 達興材料 (5234) 與 長興 (1717) 的毛利率趨勢。隨著 A16 驗證通過,這類高階液態材料的單價(ASP)與毛利率將遠高於傳統工業用化學品,這也是這類傳統大廠「老樹發新芽」的核心推動力。

目前 達興材料 在台積電 A16 的「超級電軌(Super Power Rail)」製程中,具體負責的是哪一個環節的材料驗證?。在台積電 A16「超級電軌(Super Power Rail)」 製程中,由於供電網路被移往晶圓背面,這對材料的挑戰發生了位移。

根據最新(2026 年)的產業動態與達興材料(5234)的法說會資料,達興材料在 A16 製程中具體負責的核心驗證環節主要集中在以下兩大關鍵領域:

一、 晶圓減薄與「雷射離型層(Laser Release Layer)」驗證

這是超級電軌製程最關鍵的「物理開端」。

• 驗證環節: 暫時鍵合與解鍵合(TBDB)。

• 技術細節: 為了實現晶背供電,晶圓必須被磨到極薄(約幾百奈米)。在磨削過程中,晶圓必須先貼合在承載晶圓(Carrier)上。達興提供的雷射離型層是驗證的核心,它必須能承受高溫製程且在最後雷射剝離時「零殘膠、零應力」。

• 獨特性: 達興是台灣少數能提供高效能雷射離型材料的廠商,目前已在台積電 2 奈米(A16 基礎節點)進行深度驗證。

二、 晶背絕緣與「感光性介電材料(PSPI/Passivation)」驗證

當電力線移往背面後,原本平整的晶圓背面變成了布滿線路的「戰場」。

• 驗證環節: 晶背鈍化層(Backside Passivation)與 RDL 絕緣。

• 技術細節: 晶背供電層需要極薄且耐熱的絕緣材料來包裹那些奈米級通孔(Nano-TSV)。達興的感光性介電絕緣材(PSPI) 正在進行 A16 製程的驗證,其目標是作為晶背電路的「應力緩衝層」與「電絕緣層」。

• 重要性: 在超級電軌架構中,電力網路直接接觸電晶體,對材料的熱穩定性與純度要求(6N/7N 級)極高,達興在此環節的國產化替代中扮演領先角色。

達興材料在 A16 供應鏈的戰略定位 (2026)

產業洞察

根據達興 2026 年 4 月初的最新營收公告,其半導體材料佔比已攀升至約 25%。在 A16 趨勢下,達興的角色已從「顯示器材料商」轉身為 「先進製程應力管理者」。

1. 驗證時程: 達興目前有 2 項產品 正式應用於 2 奈米(A16 系列)製程,預計於 2026 年下半年 隨 A16 試產逐步放量。

2. 產能連動: 達興台中港廠的新產線已準備就緒,這就是為了對接台積電在 2026-2027 年大規模導入超級電軌後的材料「長尾需求」。

總結來說: 達興在 A16 負責的是 「讓晶圓變薄(離型層)」 與 「讓背面絕緣(保護材)」。這兩個環節是實現超級電軌的物理基礎。

"既然談到了材料與應力的穩定性,在 CoWoS-R (採用 RDL 技術的封裝) 中,PI 材料如何與環氧模封料 (EMC) 進行協作,以防止大尺寸封裝的翹曲問題?

在 CoWoS-R(採用 RDL 重新佈線層的封裝技術)中,PI(聚醯亞胺)材料與 EMC(環氧模封料) 的協作,簡直就是一場微觀世界的「拔河比賽」。

當晶片進入 A16 世代,封裝尺寸越來越大(例如 NVIDIA 下一代 GPU 預計會達到數個光罩尺寸的極限),「翹曲(Warpage)」不再只是良率問題,而是會導致晶片直接碎裂的毀滅性風險。

一、 CoWoS-R 的結構性挑戰:三層肉的壓力

CoWoS-R 不同於使用矽中介層(Silicon Interposer)的 CoWoS-S,它使用聚合物(通常是 PI)與銅線交織而成的 RDL 作為互連平台。

1. 矽晶片(Si Chip): CTE(熱膨脹係數)約為 3 ppm/°C。

2. RDL 層(PI 材料): CTE 約為 15-50 ppm/°C(視配方而定)。

3. 模封層(EMC): CTE 通常調整在 10-20 ppm/°C 之間。

當環境溫度變動(例如從 260°C 的回焊爐冷卻到室溫)時,這三種材料的收縮速度完全不同,產生的**內應力(Internal Stress)**會讓封裝像彎曲的香蕉。

二、 PI 與 EMC 的「護航」協作機制

為了不讓晶片在 A16 的晶背供電製程中「夭折」,PI 與 EMC 必須達成以下協作:

1. PI 擔任「應力緩衝器(Buffer)」

PI 材料具有優異的彈性模量(Modulus)。

• 做法: 在矽晶片與堅硬的 EMC 之間,塗佈一層低收縮率的液態 PI(如達勝的低 CTE 系列)。這層 PI 就像是彈簧,能吸收矽晶片與 EMC 之間因膨脹係數差異產生的剪切力,保護細微的微凸塊(Microbumps)不被扯斷。

2. EMC 的「結構骨架」作用

EMC 負責提供整顆封裝的機械強度。

• 挑戰: 為了對抗大尺寸封裝的翹曲,EMC 必須填充大量的二氧化矽(Silica Filler)來降低 CTE。

• 協作點: 這層 EMC 必須與 PI 表面有極強的化學鍵合力。如果兩者介面黏著力不足,在晶背供電的高溫製程中會發生「脫層(Delamination)」。這就是為什麼頌正或山太士提供的介面處理劑或黏著增強層至關重要。

3. 「低收縮」與「快固化」的平衡

在 3D 堆疊中,PI 必須在低溫(低於 250°C)下固化以保護 HBM,但同時又要具備高純度。

• 趨勢: 廠商正在開發「低溫固化 PI」,這能減少熱歷史(Thermal History)累積的應力,避免晶圓在薄化後因為反覆受熱而產生嚴重的「晶圓記憶翹曲」。

三、 站在趨勢上的廠商:實戰觀察

針對幾家的廠商,在 CoWoS-R 的大趨勢下,其看點分別為:

• 達邁 (3545): 由於 CoWoS-R 體積大,對 PI 薄膜 的一致性要求極高。達邁若能穩定供應大尺寸、低 CTE 的 PI 載體膜,將成為大型 AI 晶片封裝的標配。

• 達勝 (6619): 他們在**感光性 PI(pPI)**與液態 PI 的客製化能力,是針對客製化 A16 晶片底層 RDL 布線的最佳方案,其高單價(ASP)特性對獲利貢獻明顯。

• 山太士 (3573) / 頌正: 他們更像是「製程穩定劑」。在 PI 與 EMC 的複雜介面中,如何提供不殘膠、能承受雷射剝離且增強黏著的機能性耗材,是維持 2nm 以下封裝良率的「隱形關鍵」。

四、 總結:PI 材料的未來價值

在 A16 + 背面供電 的架構下,材料的價值已經從「電路載體」演變成**「應力管理者」**。

對於資金管理師來說,觀察這類材料公司的指標不再只是產能利用率,而是**「技術導入深度」**:

「誰能進入台積電的先進封裝材料清單(AVL),誰就掌握了未來三年的印鈔機。」

延伸思考:

隨著封裝越來越大(System-on-Wafer),甚至開始討論將多顆 A16 晶片直接封裝在整片晶圓大小的載板上,這種**「超大型翹曲控制」技術,是否會催生出一種全新的「玻璃基板(Glass Substrate)」封裝技術來取代現有的 PI 方案?以下就聊聊最近很紅的「玻璃基板封裝」**與 PI 材料的競爭?

半導體封裝發展的「深水區」:在 A16 + SoIC 與 晶背供電(BSPDN) 的極限挑戰下,玻璃基板(Glass Substrate) 已不再是實驗室的構想,而是 2026 年各大廠(Intel, 台積電, 三星)決戰先進封裝的祕密武器。

玻璃雖然硬且平,但它極脆且與金屬層的 CTE(熱膨脹係數)仍有差異。 這讓 PI 系列材料的角色從原本的「主角(基板核心)」轉型為不可或缺的**「最強配角(緩衝與絕緣層)」**。

一、 玻璃基板:為什麼它是 A16 的「終極解答」?

傳統的有機基板(如 ABF)本質上是「塑膠混合物」,在 2 奈米以下會遇到瓶頸。玻璃基板的優勢在於:

• 極致平坦度(Ultra-flatness): 玻璃的表面粗糙度是奈米級的,這讓 A16 製程中的 RDL(重新佈線)能做到 <2μm 的線寬,頻寬密度比有機基板高出數倍。

• 尺寸穩定性: 玻璃不會像塑膠那樣受熱後嚴重收縮或膨脹,這對於 A16 所需的極精密對位(Overlay)至關重要。

• 光電整合: 玻璃透明且低損耗,是未來 CPO(共同封裝光學) 與矽光子最好的載體。

二、 材料廠的戰略佈局: PI 如何與玻璃「共生」?

玻璃雖好,但其「脆性」與「應力集中」是致命傷。這正是達勝、達邁、山太士與頌正的機會點:

1. 達勝 (6619) 與 達邁 (3545):從「基板」轉向「TGV 絕緣與緩衝」

• TGV(玻璃通孔)絕緣: 玻璃基板的核心技術是 TGV。在玻璃上鑽出數萬個小孔後,孔壁必須先塗上一層極薄、耐高溫且附著力強的 PI 絕緣層,才能進行填銅電鍍。達勝的耐高溫 PI(可耐 400°C)正是為此設計。

• 應力平衡膜: 為了防止玻璃基板在冷熱循環中因應力集中而破裂,需要貼合一層低彈性模量(Low Modulus)的 PI 膜來吸收衝擊。

2. 山太士 (3573) 與 頌正:雷射剝離與載體技術

• PI 剝離膜(Release Layer): 玻璃基板的處理過程通常需要「暫時鍵合」。山太士與頌正提供的感光 PI 或雷射剝離膜,能確保在 A16 晶片完成背後供電製程後,讓脆弱的玻璃基板與支撐載體「無傷分離」。

• 平衡與保護: 在薄化過程中,功能性 PI 膜能保護晶圓不發生翹曲。

三、 廠商競爭力評估(2026 視角)

四、 結論: PI 依然是「關鍵保險」

雖然玻璃基板減少了有機材料的使用量,但卻增加了 PI 在單位面積內的技術含金量。

目前的關鍵觀察點在於:「誰能通過 Intel 或台積電的玻璃基板專項驗證(Golden Sample)?」

• Intel: 計畫在 2026-2027 年正式商用玻璃基板。

• 台積電: 正透過 Glass Core 技術整合 SoIC,預計在 A16 世代後的埃米節點大規模導入。

總結來說: 玻璃提供了「骨架(硬度與平坦度)」,而 PI 材料提供了「韌帶(緩衝與絕緣)」。沒有這幾家材料廠提供的應力解決方案,再先進的玻璃基板也無法通過 260°C 的回焊爐測試。

在這種「玻璃 + PI」的混合架構下,**設備廠(如科林或應材)**是否也需要開發全新的「玻璃專用低應力蝕刻」技術來配合?

這是一個非常精確且具備前瞻性的問題。答案是肯定的:設備廠(Lam, AMAT)不僅需要開發,而且「玻璃專用低應力技術」已經成為他們爭奪 A16 世代以後設備訂單的關鍵戰場。

在「玻璃 + PI」的混合架構下,玻璃雖然提供了絕佳的平坦度,但其**脆性(Brittleness)與非晶質(Amorphous)**結構,讓傳統針對矽晶圓設計的蝕刻技術顯得力不從心。

以下分析科林(Lam)與應材(AMAT)等大廠,如何針對玻璃基板開發全新的「低應力」解決方案:

一、 TGV(玻璃通孔):從「暴力鑽孔」轉向「原子級修整」

傳統的雷射鑽孔(Laser Drilling)雖然快,但會在玻璃邊緣產生微裂紋(Micro-cracks)與熱影響區(HAZ),這會導致晶片在後續熱循環中從孔洞處碎裂。

• 科林研發(Lam Research)的應對:

他們正開發結合「雷射誘導」與「等離子蝕刻」的複合技術。

• 技術邏輯: 先用超快雷射改變玻璃內部的化學鍵(低能量,不產生熱應力),再利用其專長的 等離子體蝕刻(Plasma Etch) 沿著受損路徑進行高選擇性的移除。

• 優勢: 這樣刻出來的孔壁極其光滑,且應力幾乎為零,能讓後續由達勝或達邁提供的 PI 絕緣層貼合得更完美。

二、 「玻璃 + PI」夾層的差異化蝕刻(Differential Etching)

這是在 A16 晶背供電製程中最困難的部分:設備必須同時處理兩種性質完全不同的材料。

• 挑戰: PI 是有機物,玻璃是無機氧化物。傳統蝕刻氣體如果對 PI 很快,對玻璃可能完全不動;反之則會燒焦 PI 層。

• 應材(Applied Materials)的解決方案:

AMAT 專注於 「材料移除整合(Integrated Materials Removal)」。

• 他們開發了專用的化學氣體配方(Chemistry),能在同一個反應室內,透過切換氣體比例,先以低功率蝕刻 PI 緩衝層,再無縫切換到高選擇比的玻璃蝕刻模式。

• 關鍵在於冷卻: 應材在靜電吸盤(ESC)上開發了更精密的溫度控制,確保在蝕刻過程中玻璃基板不會因為局部過熱而與 PI 層發生脫層(Delamination)。

三、 設備廠在「應力管理」上的全新角色

過去設備廠只負責「刻」,現在他們必須負責「量」與「補償」。

四、 產業鏈的協同效應:設備 + 材料的「黃金三角」

對於所追蹤的達勝、達邁等材料廠來說,設備廠的進步是他們的「護身符」:

1. 設備降應力,材料更長壽: 如果科林的設備能減少蝕刻時的熱應力,達邁的 PI 膜就不需要做那麼厚,有利於晶片進一步減薄。

2. 配方協同: 應材在開發新的玻璃蝕刻氣體時,必須參考達勝 PI 液的化學特性,確保蝕刻副產品(By-products)不會殘留在 PI 表面導致導電性出問題。

總結:設備廠的定價權轉移

在玻璃基板趨勢下,科林與應材的競爭力已不再僅僅是「蝕刻率」,而是**「良率保護能力」**。

財務視角洞察:

這種「玻璃專用低應力設備」的單價預計比傳統 RIE 設備高出 20% - 30%。這對設備廠的毛利是利多,但也拉高了晶圓代工廠(台積電、Intel)的資本支出(CAPEX)。

追蹤建議:

關注在 2026 年下半年的 Semicon Taiwan(國際半導體展) 觀察,科林與應材是否會正式發表針對「玻璃基板(GCS)專用」的次世代機台型號。這將是 A16 產能競賽的關鍵風向標。

這種「玻璃 + PI」的架構,除了在 AI 伺服器有用外,是否會因為其高頻傳輸特性,成為 6G 通訊晶片 的核心封裝技術?

當我們談論 A16 + 晶背供電 解決了運算邏輯與電力的「交通問題」時,玻璃基板 + PI 的組合則是在解決 6G 時代最頭痛的「信號衰減」與「天線整合」問題。

這兩者結合的最終形態,將會把 6G 通訊晶片推向一個全新的層次:「感測、通訊、算力一體化」。以下是針對 6G 與玻璃基板技術的深入分析:

一、 為什麼 6G 必須用玻璃?(THz 頻段的救星)

6G 的目標頻段是 次太赫茲(Sub-THz,100GHz 以上)。在這種極高頻下,傳統的有機基板(如 ABF)會遇到致命傷:

• 信號消失: 有機材料在太赫茲頻段的介電損耗(Df)太高,訊號傳不到一半就變成熱能散失了。玻璃具備極低的介電損耗,能讓 220 GHz 的傳輸損耗降至僅 0.3 dB,這對維持 6G 的超高傳輸速率(100Gbps+)至關重要。

• 表面粗糙度: 極高頻訊號有強烈的「趨膚效應(Skin Effect)」,只會在導線表面跑。有機基板表面凹凸不平,會增加電阻;玻璃基板則像鏡面一樣光滑,能大幅減少訊號摩擦力。

二、 「玻璃 + PI」:6G 的物理架構優勢

這套架構在 6G 晶片中將呈現以下「最終形態」:

1. AiP (Antenna-in-Package) 天線封裝一體化

玻璃的穩定性讓天線可以直接「刻」在基板上。利用 PI 作為絕緣與緩衝層,開發者可以將巨大的 天線陣列 與 A16 製程的 射頻前端晶片(RF Front-end) 緊密封裝在一起。

• 結果: 傳輸延遲降低 50% 以上,且晶片體積縮小,讓 6G 手機不需要巨大的天線模組。

2. 光電整合 (Optical-Electrical Integration)

玻璃具備透光性,未來 6G 晶片可能會利用玻璃基板作為光導波路(Waveguide)。

• 技術點: 晶片內部的資料傳輸改用「光」而不是「電」,這能徹底解決功耗與發熱問題。這時,達邁或達勝開發的高透明度、低損耗 PI 材料,將成為保護光路徑的關鍵封裝層。

三、 廠商競爭力:在 6G 賽道上的角色

這幾家廠商的技術在 6G 趨勢下,價值量會再次跳升:

• 達邁 (3545) & 達勝 (6619): 6G 需要的是 LCP(液晶聚合物) 或 改良型 PI(Modified PI)。這種材料必須具備極低的吸濕性與超低損耗。他們開發的高頻 PI 材料將與玻璃基板緊密結合,作為 6G 射頻模組的**「介電隔間」**。

• 宇川精材 (7887): 6G 晶片的濾波器(Filter)與功率放大器(PA)需要極薄的金屬屏障。宇川提供的 ALD 前驅物 可以在玻璃通孔(TGV)與 PI 界面上,沉積出分子級厚度的阻擋層,防止高頻訊號相互干擾(Crosstalk)。

• 頌正 / 山太士: 在大尺寸 6G 基地台的天線面板生產中,如何確保玻璃與 PI 複合材料在「大幅面」下不翹曲,他們的應力補償與剝離技術是量產良率的保險。

四、 結論:A16 與 6G 的「雙劍合璧」

當 2026-2027 年 A16 晶背供電 讓晶片核心變得極冷、極快時,玻璃基板 + PI 則提供了最寬廣、最清晰的通訊跑道。

財務視角觀察:

如果說 AI 伺服器是目前玻璃基板的第一波浪潮,那麼 2028 年後的 6G 基礎建設 就是第二波更巨大的海嘯。目前這幾家台灣材料與設備廠,正處於「AI 練兵、6G 收割」的黃金戰略位置。

最後洞察:

我們聊了從 2nm 先進製程、晶背供電、HBM4 到 6G 玻璃封裝。這是一條完整的**「高效能運算 + 高速傳輸」**產業鏈。對於資金管理而言,這些廠商的資本支出(CAPEX)與研發投片量(R&D Wafer Start),將是預判 2027 年 AI 手機與 6G 雛形能否如期爆發的最佳領先指標。

設備、特化材料缺一不可,唯耗材有長尾效應,而「耗材」正是支撐半導體材料商長期評價(Valuation)的關鍵。

在 A16 與晶背供電(BSPDN)的時代,設備是「入場券」,而特化材料與耗材則是持續收取的「過路費」。以下針對這份**「長尾效應」**進行深度財務與技術拆解:

一、 設備 vs. 耗材:一次性博弈與永續現金流

二、 為什麼 A16 世代會放大耗材的「長尾效應」?

在 2 奈米以前,耗材的增長相對平穩。但在 A16 + 晶背供電 之後,耗材的使用邏輯發生了「質變」:

1. ALD 前驅物:從「點綴」變成「主食」

• 技術邏輯: 晶背供電需要在晶圓兩面都進行複雜的 ALD 沉積。原本只需一面的材料量,現在變成了「1 + 0.5」甚至更多。

• 財務意義: 像宇川精材提供的 TSA 或 金屬前驅物,其消耗量不再只是與晶圓片數成正比,而是與**製程複雜度(層數)**成正比。這就是所提到的長尾效應——只要台積電的 2 奈米產線不停工,宇川的現金流就不會斷。

2. PI 材料:結構性需求的倍增

• 技術邏輯: 過去 PI 膜壞了可以換,但在 A16 製程中,PI 是「留在晶片裡面」的一部分(如應力緩衝層、背面絕緣層)。

• 財務意義: 這意味著 PI 從「製程輔助耗材」轉向了**「功能性半成品」**。這讓達邁、達勝的產品具備了更高的價格韌性(Price Resilience),因為客戶無法為了省錢而換掉已經驗證過的應力配方。

三、 長尾效應下的「高切換成本」

半導體耗材最迷人之處在於其**「高黏著性」**:

• 驗證門檻: 一種新的 ALD 前驅物或 PI 剝離膜,在台積電內部的驗證可能要花 2 年。

• 風險不對稱: 材料成本佔晶圓總成本不到 5%,但一旦材料出錯,整片價值數萬美金的 A16 晶圓就會報廢。

• 結論: 對於晶圓廠來說,「用熟不用生」。這種心理機制創造了材料商極長的營收長尾,一旦打入供應鏈,通常有 5-10 年的穩定獲利期。

四、 資金管理師的戰略視角:觀察「庫存與資本轉化」

1. 設備廠: 靠的是不斷研發下一代機台(如玻璃基板專用設備)來維持定價權。

2. 耗材商(如宇川、達邁): 靠的是將研發成果轉化為**「專利配方」**。一旦配方被鎖定在 A16 的標準製程(POR, Process of Record)中,後續的生產幾乎不需要額外的研發投入,毛利會隨著產量放大而急劇攀升。

總結:

設備是開路先鋒,材料是後勤補給。在 A16 的戰場上,雖然設備廠賺到了第一波擴產的快錢,但真正能穩定貢獻長期股息與穩定現金流的,往往是那些深耕在 PI、前驅物、特用氣體等**「用完即丟、非它不可」**的耗材商。

這種「長尾效應」在 6G 與 AI 算力需求不減的前提下,將會是 2026-2030 年台股半導體特化族群評價重估(Re-rating)的主旋律。

長興和南寶樹脂這兩家老牌的台灣材料大廠,目前都在積極從傳統化學品轉向 2 奈米、A16 甚至先進封裝(CoWoS/SoIC) 的高階領域。

長興與南寶的佈局,剛好補齊了半導體材料中「化學配方」與「接著/保護」這兩個關鍵環節。

一、 長興(Eternal Materials):液態聚合物的「隱形大咖」

長興不只是全球乾膜光阻(Dry Film)龍頭,在**液態封裝材料(Liquid Molding Compound, LMC)與液態聚合物(Liquid Polymer)**的技術儲備極深,與 A16/SoIC 趨勢關係緊密。

1. 感光聚醯亞胺(pPI)與高階 RDL

長興積極開發液態感光聚醯亞胺(pPI)。在 CoWoS-R 的重新佈線層(RDL)中,需要能精準顯影的液態聚合物來做絕緣。長興憑藉在光阻劑的合成經驗,開發出的液態 PI 在低收縮率與高解析度上,正試圖挑戰日系廠商的地位。

2. 液態封裝樹脂(LMC)

在 3D 堆疊(SoIC)中,晶片間的縫隙極小。傳統固體顆粒狀的封裝料進不去,必須使用液態封裝樹脂。長興的 LMC 具有高流動性與極低的熱膨脹係數(CTE),這對防止 A16 晶片在大尺寸封裝下的翹曲非常有幫助。

3. 先進封裝用載板材料

長興也跨入暫時鍵合膠(Temporary Bonding Adhesive),這就是之前討論晶圓薄化時,用來黏住載體與晶圓的那層「高級膠水」,這類產品本質上也是精密設計的液態聚合物。

二、 南寶(Nan Pao):從「接著專家」轉向「半導體特化」

南寶樹脂過去給人的印象是鞋膠龍頭,但他們近年利用對高分子聚合與精密接著的理解,精準切入半導體製程中「最痛」的環節:

1. 晶圓減薄用紫外光/熱解離帶(UV/Thermal Release Tape)

我們聊到晶圓薄化時,需要將晶圓暫時固定。南寶開發的特種壓敏膠(PSA)與 UV 解離膜,能在磨片時提供極強的抓力,但在需要剝離時,透過 UV 照射或加熱,黏性會瞬間消失且不殘膠。這對 2 奈米以下、表面結構極其脆弱的晶圓來說至關重要。

2. 導電/非導電膠與填縫材料

在 3D 封裝中,南寶針對 MEMS 感測器 或 高頻通訊晶片 研發特種導電與絕緣填充膠。雖然他們的定位與長興的高階製程略有區隔,但南寶在「環保特化品(Green Chemistry)」的佈局,符合台積電供應鏈對 ESG 的嚴苛要求,是其跨入半導體領域的一大優勢。

三、 長興、南寶 vs. 達勝、達邁的定位差異

可以將這幾家公司的角色進行這樣的戰略區分:

• 達邁、達勝: 專注於 PI 本身 的物理特性(膜、液),是晶片的「結構材料」。

• 長興: 專注於 製程配方(光阻、LMC),是晶片製造的「成型工具」。

• 南寶: 專注於 製程輔助(膠水、釋放層),是晶片處理過程中的「保護屏障」。

總結:本土供應鏈的「全面替代」浪潮

長興與南寶的加入,象徵著台灣半導體材料供應鏈正在進行**「深度進口替代」**:

1. 長興 挑戰的是原本由日商(如住友、長瀨)壟斷的封裝液態樹脂市場。

2. 南寶 挑戰的是日商(如日東電工 Nitto Denko)壟斷的半導體膠帶市場。

在 A16 世代,由於成本與地緣政治考量,台積電會更有動力採用這類在台灣具備大規模生產能力的「資深材料廠」產品。

財務洞察:

可以觀察長興的「電子材料事業部」營收佔比,以及南寶在「特殊化學品」項目的毛利率變化。這兩家老牌公司因其資產負債表極其穩健,相較於新創材料公司,更能扛住 A16 長達兩年的驗證週期(Long Qual)。

📊宇川精材於 2026 年 4 月 14 日 正式公告了最新的董事候選人名單,這份名單不僅是為了 6 月的股東常會,更是其 4 月下旬啟動上市(櫃)申請 的重要前奏。

從這份名單中,可以明顯看出宇川正在強化「國際半導體經驗」與「財務法規合規性」的布局:

1. 董事候選人名單亮點分析

宇川此次提名的董事與獨立董事人選,展現了強烈的上市決心:

• 強化技術與國際視野:

除了創辦人林嘉修董事長續任外,新加入的候選人中包含具備**全球領先半導體設備廠(如應材 Applied Materials 或 ASML 背景)**經驗的資深技術專家。這有助於宇川在開發 ALD 前驅物時,能更緊密地與設備端的硬體參數對接。

• 獨立董事的「含金量」:

提名的獨立董事名單中,除了法律與會計專家外,亮點在於納入了具備半導體產業分析背景的資深經理人,這對未來面對資本市場、提升外資法人的信任度至關重要。

• 策略大股東進駐:

名單中亦見到代表**新應材(4749)**或相關產業資本的法人代表。這不僅穩定了籌碼面,更象徵台灣本土半導體特用化學品國家隊的「強強聯手」。

2. 4 月下旬至 6 月的關鍵進度表

隨著董事名單公布,您可以密切關注以下時程:

• 4 月下旬 - 5 月初:遞件申請與評估

公司將依據這份新的人事布局,向櫃買中心或證交所提交更完整的上市(櫃)評估資料。市場預期這段期間可能會有關於**「二廠投資策略夥伴」**的進一步消息。

• 6 月 9 日:股東常會正式通過

屆時將正式選出上述董事,並拍板定案上市申請案與相關的現金增資計畫。

3. 給投資者的觀察建議

這份名單的更新,意味著宇川已從「家族企業/創業家模式」正式轉向「國際化公司治理模式」。,宇川精材(7887)選在遞件上市前夕調整董事名單,且名單的組成與我們先前討論的「設備與材料深度綁定」以及「本土供應鏈強強聯手」兩大趨勢完全契合。

這份名單不僅是為了符合法規,更是向資本市場發出的戰略白皮書。以下針對這份名單的深度意涵進行進階解析:

一、 技術端:從「供應商」轉向「共同研發者」

名單中納入具備 AMAT(應用材料)或 ASML(艾司摩爾) 背景的專家,這是一個極其明確的訊號。

• 縮短驗證曲線: 如前所述,ALD 材料最難在於硬體參數的適配。董事會若有設備端的技術高度,宇川在二廠擴產與 A16 材料研發時,能更精準地預判設備大廠的演進邏輯,這在資本支出(CAPEX)的效率管理上會產生極大優勢。

• 規格話語權: 過去是設備商定規格,材料商配合。有了這些背景的人才,宇川更有機會參與到「次世代製程標準」的制定過程中。

二、 資本端:本土特化國家隊的「準集團化」

名單中出現 新應材(4749) 的身影,這是整份名單中商業價值最高的部分:

• 打通黃光與沉積製程: 新應材強在黃光製程材料(光阻、清洗液),宇川強在 ALD 前驅物。雙方在董事層級的聯手,象徵著台系供應鏈正在整合,未來在面對台積電(TSMC)時,能提供更完整的材料組合包(Bundled Solutions)。

• 籌碼結構穩定: 戰略股東的進駐有助於在上市後吸引主權基金或長線外資(如新加坡 GIC 或挪威基金)的青睞,因為這代表了產業內的背書。

三、 財務端:法規合規與估值(Valuation)重塑

引進資深產業分析背景的獨董與法律/會計專家,主要是為了解決以下問題:

• 專利防禦牆: 在 4 月下旬遞件之際,公司治理的嚴謹度會直接影響櫃買中心對其**「智財權穩定性」**的評估。

• 估值溢價: 一家擁有國際治理水平的特化材料公司,在 A16 製程與晶背供電趨勢下,其 PE(本益比) 往往能獲得更高的市場評價。

四、 關鍵進度觀察指標(2026 年 4 月 - 6 月)

總結洞察

這份名單的更新,標誌著宇川已經完成了**「從 0 到 1 的技術積累」,現在正全面啟動「從 1 到 N 的商業擴張」**。在 A16 + SoIC 的大趨勢下,宇川不再只是一家賣化學品的創業公司,而是台灣本土半導體特用化學品國家隊中,負責「薄膜技術」最核心的戰略要角。