📋 核心規則摘要

- Rule: 效能最佳化只在生存邊界以內進行。這條規則在 IC design review 成立,在投資風控也成立。

- Mechanism: IC 設計和投資管理面對同一個根本問題,在不可預測的環境中設計必須長期存活的系統,而兩個領域獨立發展出幾乎一樣的解法。

- Boundary: 這套思維適用於以存活為前提的長期資本配置者。如果你的目標是短期極大化報酬、或者你的資金有明確的到期壓力,容錯設計的「冗餘成本」會拖累你的效能。

- Trade-offs: 路徑 A 是全面導入容錯框架,代價是放棄部分極端績效;路徑 B 是選擇性採用,代價是保護不完整;路徑 C 是不採用,代價是你押注自己永遠不會遇到設計邊界以外的情境。

- Misread Guardrail: 這篇文章交付的是設計哲學,不是交易系統。讀完不會讓你多賺一塊錢,但可能讓你在該活下來的時候活下來。

兩個產業,同一道存活題

如何設計一個失敗的代價極高的系統,讓它在你無法預測的環境中長期運作?

我在兩個完全不同的領域各花了超過十年,才意識到自己一直在解同一道題。

第一次是在半導體產業。從 IC 驗證、tape-out、ECO 到客戶端量產,再到 Synopsys 補齊設計端和 IC 驗證的完整視角。第二次是在投資。從建構自己的風控框架,到真金白銀在市場裡測試每一條規則。

這兩個領域的人平常幾乎不對話。但他們面對的根本問題一樣,而且真正驚訝的部分,是他們各自發展出來的解法,結構上幾乎一模一樣。

這不只是比喻。這是同一類存活問題,在不同系統裡長出的相似設計原則。

IC 設計師怎麼讓晶片活下來

做過 IC 的人都知道,晶片送去 fab 之後,你能改的東西極有限。晶片不會給你第二次機會重新設計 base layer。所以整個設計哲學的核心,從第一天就不是「怎麼跑最快」,而是「怎麼確保在各種意外狀況下不會壞掉」。

這個哲學體現在四個設計原則上。

第一,留冗餘 (Design Margin)。 沒有哪個合格的 IC 設計師會把元件操在理論極限。電壓和 timing 都會保留 guard band,你在規格書上看到的數字,和實際設計的數字之間永遠有一段緩衝。因為真實世界的製程變異 (process variation) 一定會超出模型預測,你不知道會往哪個方向偏,但你知道一定會偏。

第二,確保訊號不失真 (Buffer)。 訊號從 A 點傳到 B 點,距離越遠,衰減越嚴重。Buffer 的功能是在傳輸鏈的關鍵節點上放大訊號、恢復波形,確保到了遠端還是乾淨的。沒有 buffer 的設計,短距離沒問題,一旦系統規模變大,訊號品質就崩潰。

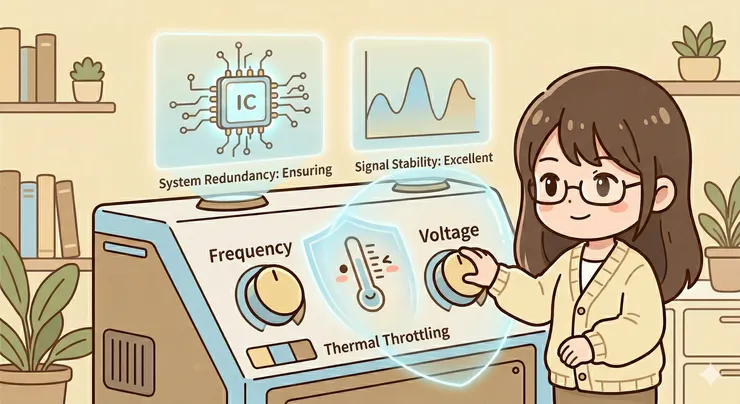

第三,動態調整 (DVFS)。 DVFS 全名是 Dynamic Voltage and Frequency Scaling,你手機裡的省電模式切換到效能模式,底層就是這個機制。關鍵在於電壓和頻率是連動的,你不能只拉高頻率不加電壓,否則會產生 timing violation,訊號來不及在時脈週期內穩定,輸出就會出錯。DVFS 的精髓是根據當下的工作負載,在效能和功耗之間即時找到最佳平衡點。重點在動態適應,根據當下條件即時調整,而不是鎖死在某個固定模式。

第四,過熱保護 (Thermal Throttling)。 當晶片的溫度或功耗逼近設計 envelope,硬體會直接觸發 thermal throttling,強制降頻。注意,這不是軟體層的建議,是硬體層的強制執行。不管你的應用程式多想跑滿速,保護機制一旦介入,沒有商量餘地。

這四個原則不是零散的技巧。它們是對同一個根本問題的系統性回應,也就是在確定性不足的環境裡,確保系統存活。

配置者面對的是同一道題

我開始做投資之後,花了好幾年才意識到一件事。

先說邊界。這套映射只適合把生存放在報酬前面的長期資本,如果你的資金有明確到期壓力,或者你追求的是短期極大化,以下的對應關係對你的意義有限。

我在風控框架裡反覆調校的那些規則:現金水位、流動性門檻、部位大小、硬停損,它們的設計邏輯和 IC 裡的四個原則完全對應。不是我刻意去套的。是我回頭看才發現,同一套直覺在指導兩邊的決策。

Design Margin 對應的是不把資金 100% 部署。 永遠留現金水位。原因一模一樣,真實世界的波動一定超出你的模型能預測的範圍。你不知道黑天鵝從哪來,但你知道牠一定會來。margin 不是浪費,是存活的前提。

Buffer 對應的是流動性儲備。 只交易高流動性的標的,確保在壓力時刻你還有能力做決策,而不是被迫在最差的時機出場。IC 裡 buffer 確保訊號到遠端不失真;投資裡流動性確保你的判斷在壓力下還能被執行。沒有流動性的部位,就像沒有 buffer 的長距離訊號線,平常看起來沒事,壓力一來就崩潰。

DVFS 對應的是動態風控。 這是我覺得對應最精準的一組。

頻率那個旋鈕,對應的是根據 conviction level 動態調整部位大小。conviction 高的時候,部位可以大一點;conviction 下降,部位跟著縮。電壓那個旋鈕,對應的是工具的保護結構,隨著風險水準同步升級。

關鍵是這兩個旋鈕必須連動。IC 裡你不能只拉頻率不加電壓,否則 timing violation;投資裡你不能只放大部位不升級工具的保護結構,否則一個跳空就把你打穿。

我們的做法是 DVFS,在晶片不燒掉的前提下,動態找到最佳效能點。

TDP 對應的是最大可承受虧損。 這是硬天花板,絕對不能突破。

而 Thermal Throttling 對應的是硬停損。 到了就砍,不是判斷層的決策,是機制層的保護。溫度到了晶片自動降頻,虧損到了系統自動停損出場。兩邊的設計精神完全一致,機制保證生存,判斷最佳化收益。這兩件事不在同一層,不能混在一起。

最後一個,也是我認為最容易被忽略的。

Timing Violation 對應的是部位超過 conviction 能支撐的範圍。

IC 裡的 timing violation 不會讓晶片馬上壞掉。它會產生偶發的錯誤輸出。有時候對,有時候錯,看起來系統還在運作,但輸出品質已經在惡化。如果你不抓出來修,累積到一定程度,整個系統的可靠性就完了。

投資裡,部位太大也不一定馬上爆倉。但你的決策品質已經在惡化了。你開始更頻繁地看盤,開始對噪音反應過度,開始在該加碼的時候猶豫、該停損的時候拖延。表面上帳戶還在,但裡面的決策引擎已經不可靠了。

壞掉是慢慢累積的。等你發現的時候,往往已經太晚了。

從 Simulation 到 Silicon,整條流程的啟示

大部分投資文章講到回測和實際交易的差距就停了。但走過 IC 完整流程的人知道,問題遠不只出在這一層。

IC 的生命週期是這樣的。最上層是 firmware 和 spec,也就是你要這個系統做什麼,對應投資裡的策略邏輯開發。接下來是 IC 驗證,在模擬環境裡確認設計意圖能不能 work,對應回測和 paper trading。然後是 tape-out,設計送出去了,不可逆,對應實際交易建立部位。再來是 ECO (Engineering Change Order),在已經生產出來的矽片上做有限度的修正。最後是客戶工廠量產。

simulation 通過不代表 silicon 一定 work。

這在 IC 業界是常識。模擬環境無法完美複製真實世界的所有 corner case。Post-silicon debug 的存在本身就是這個事實的證明,如果 simulation 能捕捉一切,我們根本不需要 post-silicon debug 這個階段。

對應到投資,回測跑得再漂亮,遇到歷史上沒出現過的市場結構,策略可能直接失效。2020 年 3 月的流動性危機、2022 年英國退休金的 LDI 崩盤,都不在任何標準回測的情境裡。

走完整流程的人會發展出一種直覺,也就是風險不會只在你看得到的那一層出現。它可以從 firmware 的邏輯錯誤一路傳染到客戶端的量產良率;也可以從一個你沒注意到的宏觀假設,一路傳導到整個投資組合的存亡。

層與層之間會互相傳染。這是只做一段的人很難體會的。

所以我們的設計哲學很簡單,我們不相信模擬能捕捉所有 corner case。我們的系統本身就有容錯能力。即使遇到 simulation 沒覆蓋到的情境,晶片不會燒掉,資本不會歸零。

這不是比喻

退一步看,IC 設計和投資風控共享的,是同一條設計哲學。

在確定性不足的環境裡設計可靠系統,核心不是追求最佳效能,而是確保最差情況下系統仍然存活。效能最佳化只在生存邊界以內進行。

這句話拿去 IC design review 講,成立。拿去描述一個 family office 的風控哲學,也成立。兩邊的人聽了都會點頭,因為他們各自被真實世界教過同一課。

走完 IC 完整流程再走進投資這一行,有些直覺是自然長出來的。你不會把系統操在理論極限,因為你見過 process variation 怎麼把模擬裡完美的設計在量產時搞砸。你不會省掉 buffer,因為你見過訊號在傳輸中怎麼衰減。你不會跳過停損機制,因為你見過沒有 thermal throttling 的晶片怎麼把自己燒掉。

這些不是從書上讀來的原則。是被矽片教過一遍,再被市場教一遍,兩邊的傷疤剛好長在同一個地方。

選項與代價

路徑 A — 全面容錯。 從設計階段就把 margin、buffer、DVFS、硬停損全部建進去。代價是你永遠跑不到理論最大報酬,因為系統的一部分資源被分配去做保護而不是做進攻。適合以長期存活為第一優先的資本配置者。

路徑 B — 選擇性採用。 挑你認為最重要的幾項(比如硬停損和現金水位),其他彈性處理。代價是保護不完整,壓力測試時可能發現漏洞在你沒設防的那一層。適合有明確風險偏好、且能承受局部失效的配置者。

路徑 C — 不採用。 把所有資源投入效能最佳化,不留冗餘。代價是你在押注一件事,也就是你的模型已經覆蓋了所有 corner case,而真實世界不會給你驚喜。IC 設計師不會這樣設計晶片。但投資人做這個選擇的比例,比你以為的高很多。

⚠️ 這篇文章交付的是設計哲學,不是交易系統。文中的 IC 類比用於說明思維框架,不構成任何投資建議。你的風險承受度、資金結構和工具箱跟我不一樣,判斷需要自己做。

本文為作者的投資哲學思考,旨在交付認知框架而非具體操作建議。文中提及的技術概念與投資現象僅作為規則說明的背景,不構成任何買賣建議。每位讀者的財務狀況、風險承受度與投資目標不同,應獨立判斷文中規則的適用性。

Kuan H. Wang Miyama Capital 創辦人 / CIO