Youtube : AI的隱藏引擎:解析晶心科技

投資摘要(Executive Summary)

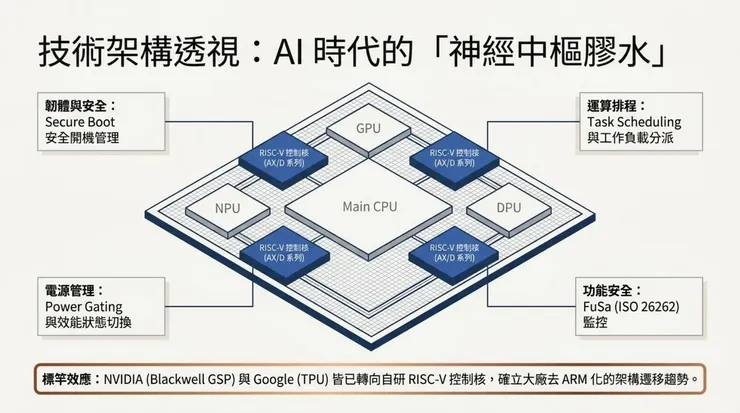

一、產業地位與 RISC-V 生態系角色

1.1 全球 RISC-V IP 市場格局

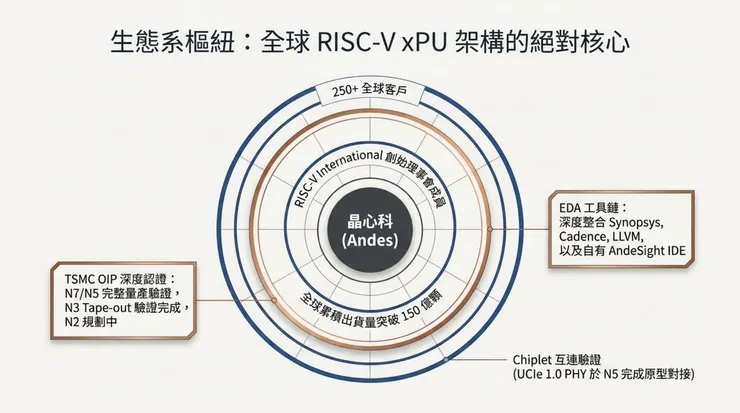

RISC-V 架構自 2010 年由加州大學柏克萊分校發布以來,已從學術計畫演變為全球半導體生態的重要基石。根據 RISC-V International 統計,截至 2025 年底全球 RISC-V 核心出貨量累計突破 150 億顆,其中嵌入式 MCU、儲存控制器、AI 推理加速器三大應用領域是主要驅動力。

晶心科(Andes Technology)成立於 2005 年,是全球最早商業化的 RISC-V 處理器 IP 廠之一,更是 RISC-V International 創始理事會成員,在生態系建構的話語權上遠超多數競爭對手。其市場地位可從三個維度理解:

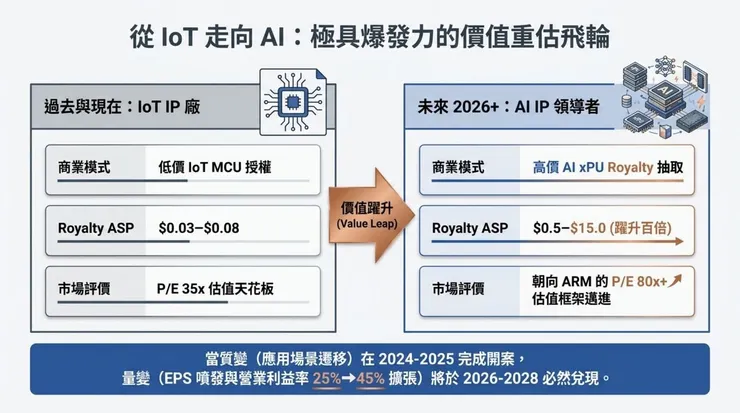

1.2 異質運算架構中的「神經中樞膠水」角色

AI 推理時代的晶片架構已不再是單一大型 CPU 主導的同質架構,而是以 xPU 為核心的 異質運算(Heterogeneous Computing) 生態。每顆 xPU(GPU/NPU/DPU/IPU)內部均需要一個輕量級控制核(Control Plane Core)來負責:

• 韌體啟動與安全開機(Secure Boot)管理

• 運算任務排程(Task Scheduling)與工作負載分派

• 與主 CPU 間的通訊協議處理(PCIe/CXL/UCIe)

• 電源管理(Power Gating)與效能狀態(P-State)切換

• 錯誤偵測與功能安全(FuSa, ISO 26262)監控

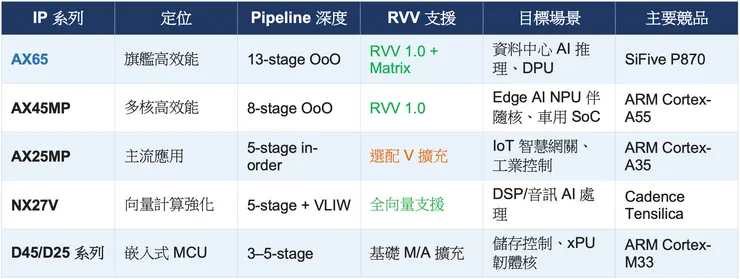

在此架構中,ARM Cortex-M 系列過去長期壟斷此控制核位置。然而,隨著 NVIDIA 在 Blackwell GPU 中採用自研 RISC-V(Falcon/GSP)、Google TPU 同樣內嵌 RISC-V 控制核,一個結構性遷移正在發生:xPU 大廠從 ARM 轉向 RISC-V,以追求 無架構授權費束縛(Royalty-Free ISA)、更高客製化彈性(ACE 擴充) 以及更好的面積功耗效率(PPA)。

晶心科的 AX 系列(AX45MP、AX65 等)正是為此場景設計。其 純量(Scalar)+向量(Vector,RVV 1.0)+可選矩陣(Matrix) 的三層次協同架構,使同一顆 SoC 上的 RISC-V 核心可同時扮演:(1) 管理核(純量運算,低功耗常駐);(2) 向量加速協處理器(RVV,處理 INT8/FP16 輕量推理任務);(3) 矩陣擴充核(與 NPU 協同,處理 Transformer attention 計算)。此三位一體的架構設計,使晶心科得以在不增加授權核數的情況下,大幅提升 Royalty 單價的議價空間。

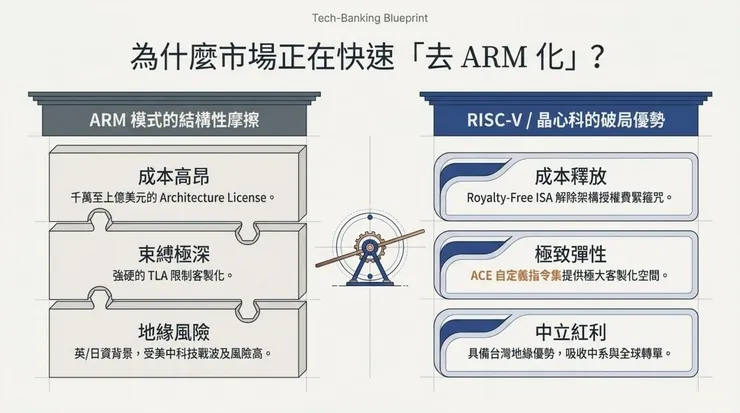

1.3 地緣政治驅動的去 ARM 化紅利

ARM Holdings 雖於 2023 年重新上市,但其授權模式對晶片設計廠商而言存在三大結構性摩擦:(1) 架構授權費(Architecture License)高達數千萬至上億美元;(2) 每顆晶片均需支付 Royalty,且 ARM 單方面調漲價格的爭議不斷;(3) 英國/日本軟銀母公司背景,在中美科技戰中存在潛在供應鏈風險。RISC-V 的開放 ISA 特性恰好解除前兩項成本壓力,晶心科則提供現成商業化 IP,補足 RISC-V 在工具鏈、驗證流程、技術支援上的短板,成為去 ARM 化浪潮中最具執行力的受益者。

二、與晶圓代工及 EDA 大廠的策略結盟

2.1 TSMC OIP 合作深度分析

晶心科是 TSMC「開放創新平台(OIP, Open Innovation Platform)」的核心 IP 合作夥伴,這一地位賦予其在全球最先進 AI 晶片製程上的絕對先發優勢。OIP 生態系的 IP 認證意義在於:任何 Fabless 廠商使用 TSMC 代工時,均優先採用已通過 OIP 認證的 IP,以縮短設計週期並降低流片風險。

N2 製程認證時程的戰略意義:TSMC N2 預計 2025 年底至 2026 年初量產,下一世代 AI 推理 SoC 的設計開案窗口約在 2025Q2–2026Q1 間集中。晶心科若能在此窗口前完成 N2 OIP 認證並進入 PDK(製程設計套件),可鎖定未來 3–4 年最高端 AI 晶片的控制核份額。

2.2 EDA 工具鏈整合優勢

晶心科在 EDA 生態的深度整合是其技術護城河的重要組成部分:

• Synopsys:完整的 DesignWare IP 協同設計流程,覆蓋從 RTL 合成、時序分析到物理驗證的全鏈路工具支援。

• Cadence:Genus/Innovus 合成布局工具完整對接,Spectre 電路模擬支援 AX 系列標準元件庫。

• Andes IDE(AndeSight):自有整合開發環境,提供客戶從 IP 整合到韌體開發的一站式工具,降低設計導入門檻。

• LLVM/GCC 工具鏈:完整支援 RISC-V 官方工具鏈,並為 ACE 自定義指令集提供編譯器擴充支援。

2.3 Chiplet 互連場景下的 PPA 驗證

隨著 AI 晶片向 Chiplet 架構演進(TSMC CoWoS、SoIC,以及 Intel EMIB 等),晶心科的 IP 需要在 UCIe(Universal Chiplet Interconnect Express) 與 BoW(Bunch of Wires) 等 Die-to-Die 互連情境下完成 PPA(功耗/效能/面積)驗證。目前已知進度:UCIe 1.0 實體層 PHY 對接驗證已在 N5 平台完成原型設計,N3 平台驗證中。此一佈局使晶心科 IP 得以在多晶粒(Multi-Die)AI 推理系統中擔任「膠水核心」的角色,橋接各異質計算晶粒之間的控制面通訊。

三、核心產品競爭力與技術節點

3.1 主要 IP 系列技術矩陣

3.2 NPU Companion Core 場景競爭力

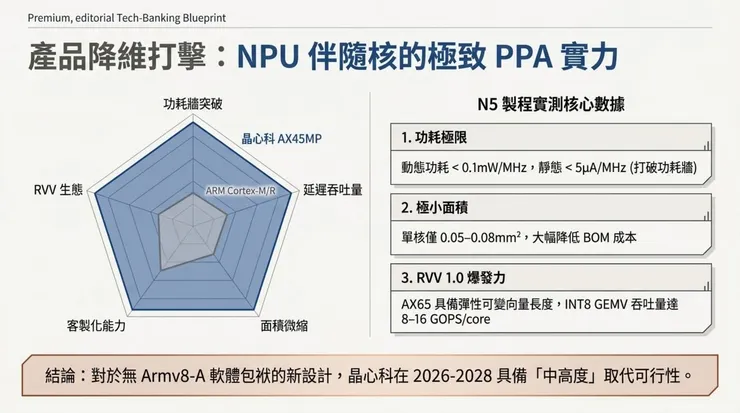

在 Edge AI 推理晶片(手機 NPU、車用 ADAS、工業 AI 加速器)中,RISC-V 作為 NPU 的 排程控制器(Dispatch Controller) 與 韌體執行核(Firmware Core) 是最關鍵的輕量伴隨核場景。關鍵評估維度:

競爭維度 晶心科 AX45MP ARM Cortex-M/R 系列

3.3 RVV 1.0 × AI 推理加速

RISC-V Vector Extension 1.0(RVV 1.0)是 RISC-V 架構在 AI 推理加速上最重要的技術突破。RVV 的可變向量長度(VLEN)設計使同一套指令集可在 128-bit 到 1024-bit 向量寬度間彈性調整,對比固定 SIMD 寬度(如 ARM NEON/SVE)更能適應不同 xPU 設計的硬體資源。

• INT8 推理吞吐量:AX65 在 1GHz 下,RVV INT8 GEMV 吞吐量可達 8–16 GOPS/core(依 VLEN 512/1024 設定),可與 Cortex-A78 相近水準競爭。

• FP16 推理:AX65 支援 RISC-V Zfh(Half-Float)擴充,FP16 GEMM 效能約為 INT8 的 50–60%,適用於精度敏感型推理場景。

• MLPerf Inference 指標:晶心科尚未有公開 MLPerf 官方提交,但內部 SPEC CPU 基準測試顯示 AX65 在 N5 製程下可達約 5.0 CoreMark/MHz,競爭力達 Cortex-A55 水準。

• 軟體生態系對接:已與 TensorFlow Lite(TFLM)完成 RISC-V 後端驗證;ONNX Runtime 的 RISC-V 後端整合進行中;FreeRTOS/Zephyr RTOS 的 BSP 支援完整。

3.4 DPU / 智慧網路卡場景

資料中心 DPU(Data Processing Unit,如 Marvell OCTEON、Broadcom Stingray、NVIDIA BlueField)的興起,代表 CPU 卸載(CPU Offloading)成為資料中心架構的標準配置。DPU 內部需要大量嵌入式核心處理:封包解析、安全加密(IPsec/TLS)、虛擬化(VirtIO)管理。晶心科的 D45/AX25MP 系列已作為 DPU 管理核的候選 IP,並在若干中大型網路晶片廠的 RFQ(詢價)流程中。此場景的 Royalty ASP 約 $0.3–$1.0/unit,量產規模相對 NPU 較小,但合約單價較高。

四、獲利模式與財務結構分析

4.1 三層次營收架構

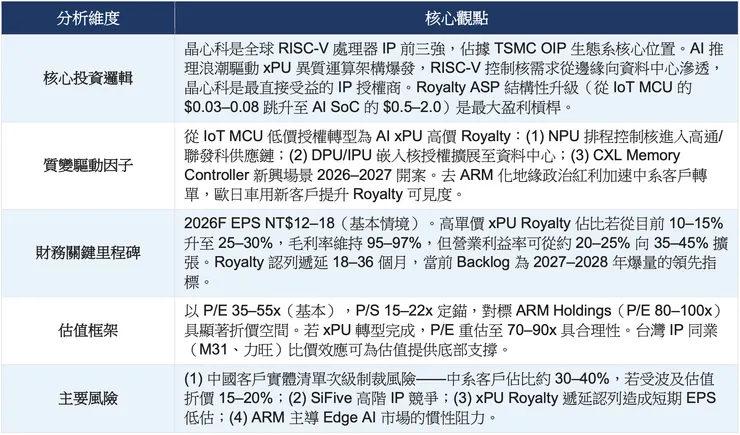

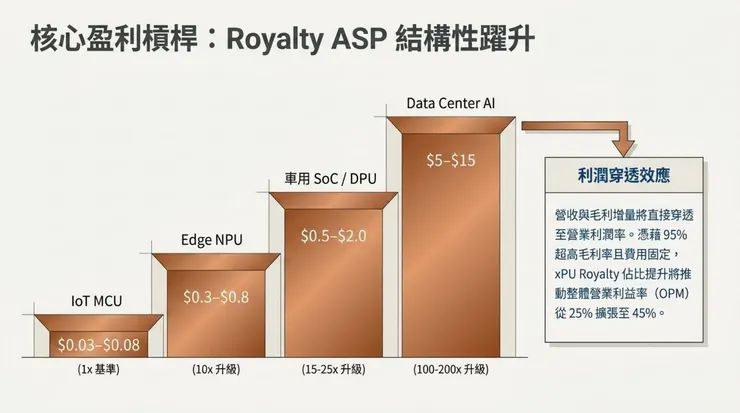

4.2 Royalty ASP 結構性升級——核心盈利槓桿

這是晶心科估值重塑的最核心驅動力。過去 Royalty 收入以 IoT MCU 為主(ASP $0.03–$0.08/unit),現在正向高單價 xPU 場景遷移:

財務推演:若高單價 xPU Royalty 佔比從目前約 10–15% 提升至 30–40%,假設整體 Royalty 收入規模維持,毛利率仍在 95–97% 高原,但 營業費用(R&D + SGA)相對固定,Royalty ASP 升級等同純粹增量毛利直入營業利潤。估算若 Royalty 年收入從 NT$300M 增長至 NT$600–900M(xPU 貢獻拉升),且授權金收入同步成長,則整體 營業利益率可從目前約 20–25% 向 35–45% 擴張,對 EPS 的邊際貢獻極為顯著。

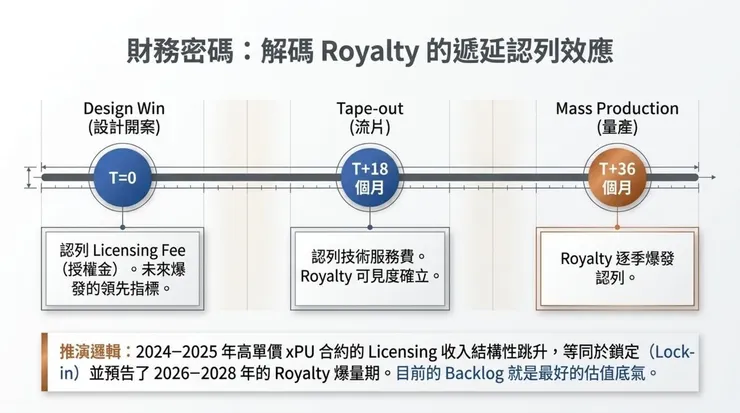

4.3 Royalty 遞延認列週期——Backlog 解讀

IP 授權業的認列週期是理解晶心科財務數字的重要框架。從設計開案(Design Win)到 Royalty 實際認列,典型路徑如下:

解讀意涵:若 2024–2025 年晶心科 Licensing 收入出現結構性跳升(特別是 xPU 相關授權),則對應的 Royalty 爆量期應落在 2026–2028 年,這與 AI 推理 SoC 量產周期完全吻合。當前帳上的授權合約 Backlog 及未認列收入(Deferred Revenue),是最重要的領先估值錨定指標。

五、終端應用與大客戶動能

5.2 地緣政治影響——中系客戶策略

中國市場是晶心科的重要營收來源,估算佔比約 30–40%。在美中科技戰背景下,中系客戶採用 RISC-V IP 存在「去 ARM 化、去美化」的強烈動機,短期對晶心科形成轉單紅利。然而,此一紅利亦伴隨潛在尾部風險:

5.2 地緣政治影響——中系客戶策略

中國市場是晶心科的重要營收來源,估算佔比約 30–40%。在美中科技戰背景下,中系客戶採用 RISC-V IP 存在「去 ARM 化、去美化」的強烈動機,短期對晶心科形成轉單紅利。然而,此一紅利亦伴隨潛在尾部風險:

5.3 日韓歐系新興客戶機會

• Sony(日本):車用 CMOS Image Sensor 後端 ISP 及 AI 邊緣運算晶片設計中有採用 RISC-V 控制核的潛在需求,晶心科的車用 ISO 26262 認證 IP 是主要加分項。

• Renesas(日本):全球車用 MCU 龍頭,正積極布局 RISC-V 架構以降低 ARM 依賴,晶心科是其潛在 RISC-V IP 合作夥伴(Renesas 已對外宣示 RISC-V 投入策略)。

• Bosch / Infineon(德國):工業 AI 與車用 SoC 廠,在 ISO 26262 ASIL-D 認證上有嚴格要求,晶心科若完成最高等級車用功能安全認證,可打入歐系 Tier-1 供應鏈。

• Samsung / SK Hynix(韓國):AI DRAM(HBM/LPDDR)內嵌 CXL Memory Controller 場景,RISC-V 作為記憶體管理核心,2026–2027 年為設計開案窗口期。

六、主要競爭對手與差異化分析

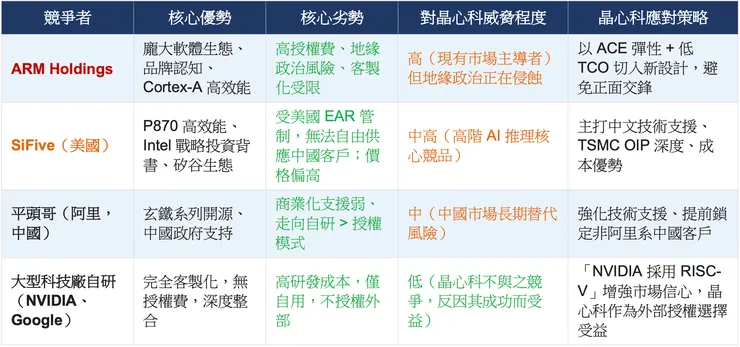

6.1 競爭格局全景

6.2 ACE 自定義指令集護城河

晶心科的 ACE(Andes Custom Extension) 是其最核心的技術差異化護城河。ACE 允許晶片設計廠商在不更改 RISC-V ISA 標準的前提下,直接在 CPU 管線內插入自定義指令,達到:

• NPU 量化載入(Quantized Load)指令:減少 INT8 張量載入的指令數,提升 NPU-CPU 資料交換效率

• 加密加速指令:AES/SHA 硬體擴充,降低 DPU/IPU 安全核面積

• 信號處理指令:定點 SIMD 擴充,優化音訊/影像 AI 前處理

• 客戶鎖定效應(Customer Lock-in):一旦客戶在其 SoC 中使用 ACE 指令,等同定製化綁定,切換競品的遷移成本極高

6.3 NVIDIA/Google xPU RISC-V 採用的啟示

NVIDIA 在 Blackwell GPU 中繼續採用 RISC-V 架構的 Falcon/GSP 微控制器(取代舊 Falcon RISC 架構),Google TPU 同樣採用 RISC-V 控制核管理 TPU 陣列排程,這兩大案例傳遞的市場信號是:頂級 xPU 設計廠商正在以「架構主權(Architectural Sovereignty)」為由,系統性地從 ARM 遷移至 RISC-V 控制核。此趨勢對晶心科的意義在於:(1) 大廠自研降低了採用 RISC-V 的認知壁壘;(2) 中小型 xPU 廠商缺乏自研能力,將轉向晶心科等商業 IP 廠;(3) 整體 RISC-V xPU 授權市場的 TAM 因此快速擴張。

七、質變/量變評價邏輯與比價矩陣

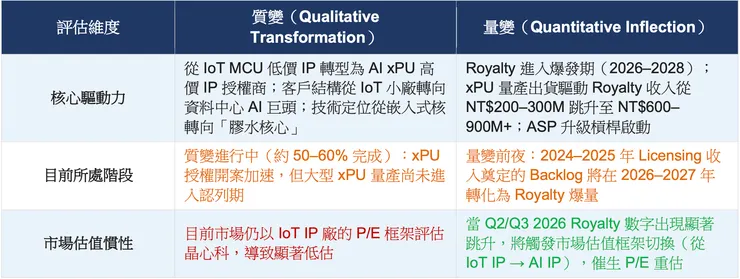

7.1 質變 vs. 量變分析框架

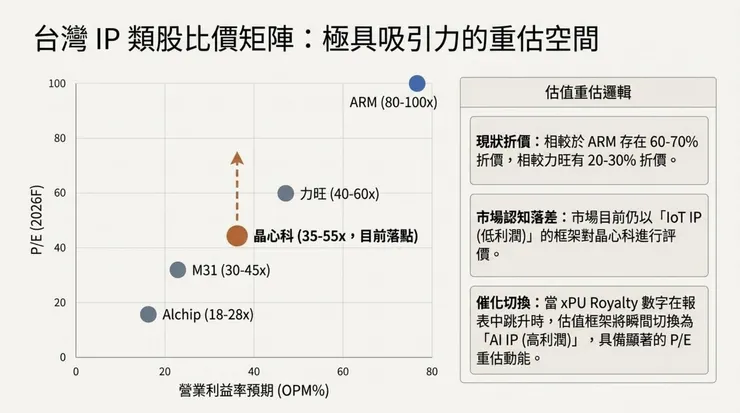

7.2 台灣 IP 類股比價矩陣(2026F)

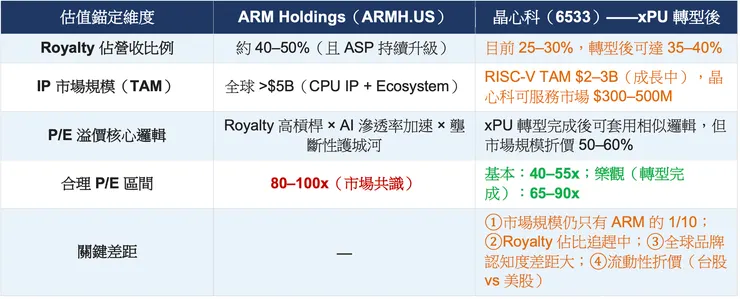

比價效應解讀:晶心科目前 P/E 相對 ARM 有 60–70% 的折價,相對力旺有 20–30% 折價。若 xPU 轉型完成,Royalty 佔比及 ASP 升級驅動 EPS 爆發,晶心科的 本益比重估空間(P/E Re-rating) 是台灣 IP 類股中最顯著的。達成 ARM 類 P/E(80–100x)的關鍵差距在於:(1) Royalty 佔比仍低於 ARM;(2) 全球品牌認知度不及 ARM;(3) 市值規模顯著較小(流動性折價)。

八、AI 推理時代的 xPU 生態系機會全景

xPU Ecosystem Opportunity Map for AI Inference Era

8.1 各場景深度分析

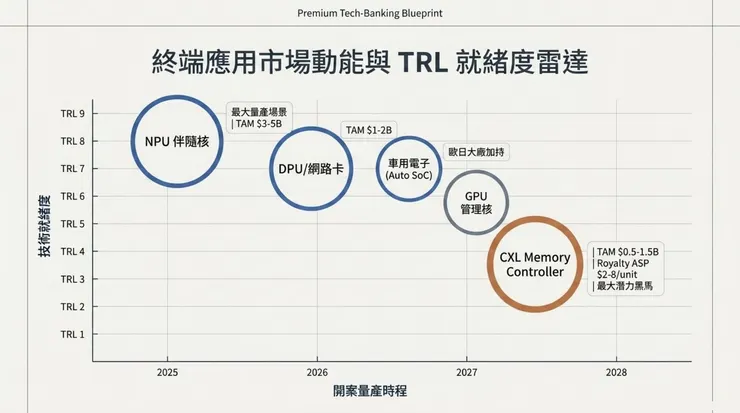

NPU Companion Core——最大量產場景

NPU 伴隨核是晶心科目前最成熟的 xPU 切入點。行動端(高通、聯發科、Apple 等)及車用(Mobileye、德州儀器)的 NPU 設計中,RISC-V 排程控制核已成標配,且多個大型客戶在 2023–2025 年已完成 Design Win,預計 2025–2027 年 Royalty 認列進入放量期。此場景的關鍵競爭點在於 PPA(以 AX45MP 為主力)及 ACE 客製指令集彈性,晶心科具備領先地位。

CXL Memory Controller——2027 年後最大潛力場景

CXL 2.0/3.0 的普及使記憶體控制器需要複雜的 QoS(服務品質)管理與 AI 訓練/推理的記憶體頻寬最佳化功能,這需要一個具備完整 OS-like 管理能力的嵌入式核。晶心科的 AX 系列在面積與功耗上相對 ARM Cortex-A 系列有競爭力,且 CXL Memory Controller 的 Royalty ASP($2–$8)是各場景中最高的之一。Samsung、SK Hynix 及台灣記憶體模組廠的 CXL 控制器設計開案,是 2026–2027 年最值得追蹤的潛力催化劑。

九、綜合估值結論

9.1 三情境估值框架(2026F)

9.2 從保守到樂觀——關鍵催化劑路徑

保守 → 基本(最可能路徑,2026H1–H2): 車用 SoC 客戶(Renesas/Sony 等)授權合約公告;Edge AI NPU Royalty 季度環比成長率超過 20%;TSMC N3 OIP 認證完成並發佈新 IP 版本。這三個催化劑若在 2026H1 出現兩個以上,即足以驅動估值框架從「IoT IP」切換至「AI IP 轉型」,P/E 重估至 40–55x。

基本 → 樂觀(高影響路徑,2026H2–2027H1): 資料中心 AI 加速器(如 Habana Labs、燧原科技、或 CSP 自研 ASIC)大規模量產並揭露晶心科為 IP 來源;CXL Memory Controller Royalty 開始認列(Royalty ASP $3–$8,直接衝擊財務認知);中國去 ARM 化替代需求爆發,Royalty 量在單季超過 NT$150M 里程碑。

9.3 與 ARM 估值差距分析

十、主要風險因素

Key Risk Factors

風險類型 評級 具體風險描述 緩解因素與估值影響