- TSMC Q1 營收年增 35% 創歷史新高,關注兩件事:2nm 製程的產能爬坡速度,以及先進封裝的擴產瓶頸。前者決定「能做多少 die」,後者決定「做出來的 die 用什麼成本組裝」。

- 先進製程:2nm已在高雄量產,良率已推進到約 70%,2026 年底月產能目標 10 萬片以上。但手機 SoC、AI GPU、CSP 自研 ASIC 同時湧入,產能仍嚴重不足。

- 先進封裝:現行 CoWoS 用圓形晶圓切大面積 interposer,面積利用率僅 45%,隨著 AI 晶片越做越大,成本只會更高。TSMC為此推出CoPoS提升封裝效率。

TSMC 四月十日公布 Q1 營收 NT$1.134 兆,年增 35.1%。三月單月年增 45.2%(史上最強的單月成長)。資優生永遠會被要求考超過一百分,這一季真正被反覆討論的不是營收成長率有多漂亮,而是兩個大哉問:第一,2nm 的產能爬坡夠不夠快?第二,先進封裝的產能卡在哪?還會卡多久?

一、2nm 量產後,產能怎麼配

TSMC 的 N2 製程已在高雄 Fab 22 量產,同功耗下效能提升 10-15%,或同效能下功耗降低 25-30%。良率推進到約 70%,預期成熟後可達 75-80%。

供給端:目前 N2 月產能約 4 到 5 萬片(高雄 Fab 22 為主,新竹 Fab 20 稍後跟進)。目標是年底合計拉到 10 萬片以上,2027 年初再推到 12.5 萬片。下半年將導入 N2P(效能增強版)和 A16(搭載背面供電技術)的量產。

需求端:過去幾個節點(5nm、3nm),基本上都是手機先行,HPC跟上。但到了 2nm,時間差幾乎沒有錯開,搶產能的隊伍比過去任何一個節點都長:

手機端:AAPL 拿走初期產能超過 50%(A20 Pro、M6 系列),QCOM 和 MTK 的旗艦 SoC 緊跟在後。

AI/HPC 端:NVDA 的 Rubin、AMD 的下一代 EPYC 和 MI 系列加速器都確認使用 2nm。

CSP 自研晶片:GOOG的 TPU、AWS 的 Trainium、MSFT 的 Maia,這些目前多在 3nm 或 5nm 的 ASIC,下一代很可能跳進 N2 來追求能效比。再加上AVGO、MRVL 的高速交換器晶片也在往更先進節點遷移。所有人幾乎同時湧入,2026 和 2027 年的 N2 產能基本被預訂一空。

能不能去別家做?

短期內很難。Intel 18A 技術上有競爭力(GAA + 背面供電),但外部客戶信心仍在建立,最快 2027-2028 才可能小規模分流。Samsung 的 2nm GAA 路線圖存在,但 3nm 良率不佳已讓 Qualcomm 等大客戶轉向 TSMC。Rapidus 目標 2027 年量產,但風險高且定位偏日本國內。2026-2027,2nm 是 TSMC 的獨佔市場。

這也解釋了 TSMC 2026 年資本支出拉到歷史新高 $52-56B 的邏輯(甚至可能增加到$60B?),超過 70% 投向先進製程(2nm、A16 擴產),約 10-20% 投向先進封裝。

法說會該聽的: N2 的 Q1 實際出貨量與良率、年底月產能目標是否上修、N2P 和 A16 的量產時程是否如期、以及 $56B capex 中 2nm 擴產與封裝擴產的比例是否有調整。

二、先進封裝-CoPoS 解方

目前 TSMC 的 CoWoS產能正以 80% 的 CAGR 擴張,產線滿載、NVIDIA 一家鎖定約 60% 產能,開始顯著放量的Google TPU亦有封裝需求,短期的供需不平衡的情況確實存在,如何在有限的資源擴大產能成了TSMC在封裝領域維持領先的最優先課題。

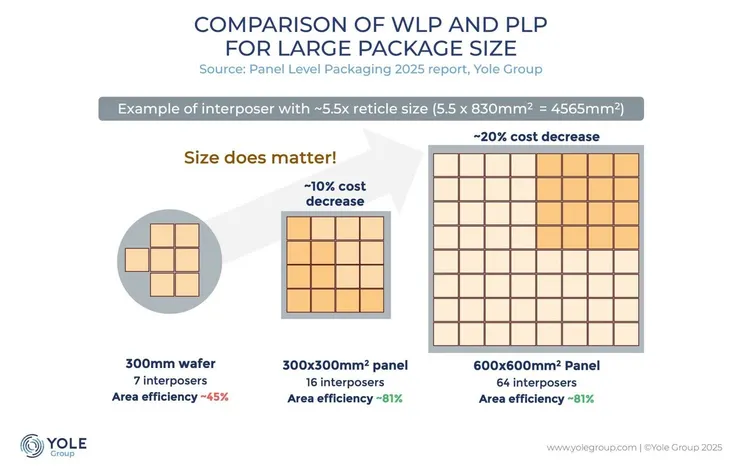

AI 晶片越做越大,NVIDIA Rubin 等級的 interposer 面積相當大。當你用 300mm 圓形晶圓來切大面積的 interposer,圓邊就顯得非常沒有效率。根據 Yole Group 的分析,一片 300mm 晶圓只能放 7 顆 5.5x reticle interposer,面積利用率僅 ~45%(超過一半的矽面積是廢料)。晶片面積還在膨脹、HBM 堆疊數量還在增加,但圓形晶圓的物理幾何不會改變,CoWoS 的單位封裝成本,會隨著 AI 晶片的演進而持續惡化。

同樣以 5.5 倍 reticle interposer 為例,300 × 300mm 方形面板可以放 16 顆,面積利用率跳到 ~81%,成本降約 10%。如果面板放大到 600 × 600mm,可放 64 顆,成本降幅達 ~20%。TSMC 的 CoPoS 初期規格 310 × 310mm,後續路線圖還有 515 × 510mm 甚至 750 × 620mm,封裝的規模經濟可以持續放大。

TSMC 的 CoPoS(Chip-on-Panel-on-Substrate)把封裝基板從圓形晶圓換成方形面板,中介層從矽轉向玻璃(更低熱膨脹係數、更少翹曲、更低成本)。4/13 TrendForce 報導,試產線已在二月進設備,預計 六月完工(子公司采鈺試產)。

CoPoS 預計 2028 年底到 2029 年 才會量產,2027 年的 Rubin 和 Rubin Ultra 仍須使用 CoWoS-L。換句話說,TSMC 已經看到圓形晶圓的經濟天花板,也已經在搶建下一代產線,但在 CoPoS 上線之前,未來兩年的封裝成本下降的可能性有限。

法說會該聽的: 管理層對 CoPoS 時程的最新說法、$56B capex 中封裝投資比重是否上調、以及是否透露 CoPoS 首批客戶的量產排程。

明天的法說會,市場固然會盯著 Q2 營收指引和毛利率展望。真正決定 TSMC 下一階段成長斜率的,是兩個問題:

1. 2nm 產能爬坡能不能跟上所有客戶同時湧入的需求;

2. 封裝成本能不能在 CoPoS 量產後降下來。

前者決定 2026-2027 年 AI 晶片出得了多少貨,後者決定 2028 年以後 AI 硬體的成本曲線往哪走。TSMC的鉅額Capex怎麼分配在這兩者之間,比總金額本身更值得著墨。