AI Computing Paradigm Revolution from Training to Inference: A Deep-Dive Report on Power, Memory, and Heterogeneous Processors (xPU) Demand Progression”

人工智慧生命週期技術轉型與資源重構

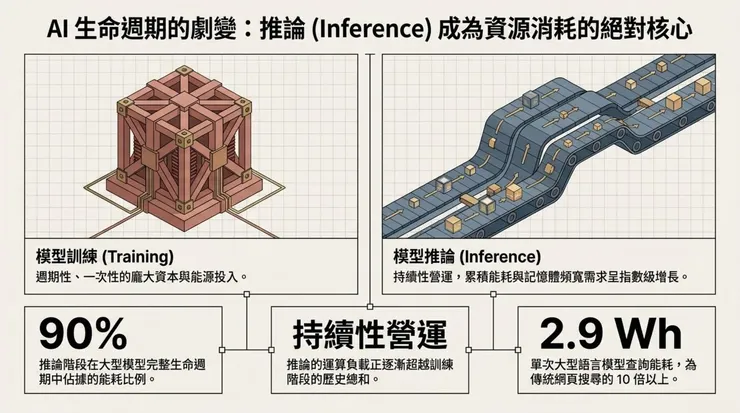

人工智慧(AI)的演進已將計算科學帶入一個全新的維度,其生命週期明確地分化為訓練(Training)與推論(Inference)兩個截然不同的階段。訓練階段是智慧的起源,涉及數據特徵的提取、模型的優化與參數的精確調整,其本質是通過海量數據的反覆計算來構建模式識別能力。在此階段,運算負載呈現出極高的並行性與計算強度,要求硬體能夠處理數百萬計的數據點,並通過反向傳播(Backpropagation)與梯度計算不斷修正模型權重。相較之下,推論階段則是將訓練完成的智慧應用於現實場景,其重點在於處理新數據並生成預測、分類或生成式內容 。

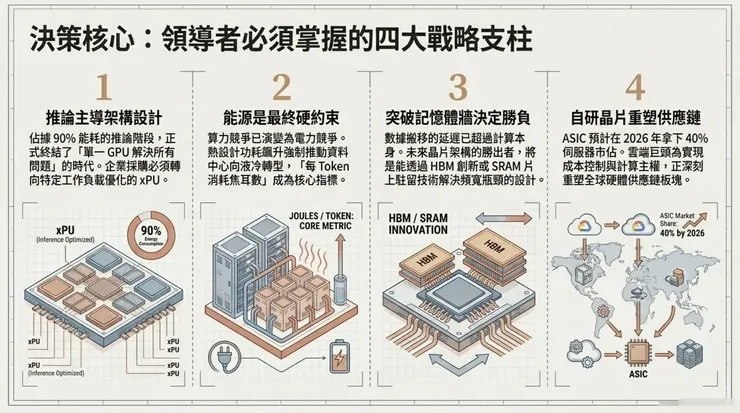

隨著生成式 AI(GenAI)與大語言模型(LLM)的爆發,硬體需求的正心正在發生深刻偏移。訓練階段雖然需要巨大的資本支出與能源投入,但通常是週期性或一次性的;而推論則是持續性的營運過程,其累積的能源消耗、記憶體頻寬需求與硬體部署規模正逐漸超越訓練階段。研究顯示,在大型模型的完整生命週期中,推論階段可能佔據高達 90% 的能源消耗。這種需求結構的轉變,推動了處理器架構從通用的圖形處理器(GPU)向更為專業的神經處理器(NPU)、語言處理器(LPU)以及各類特殊應用集成電路(ASIC)演進。

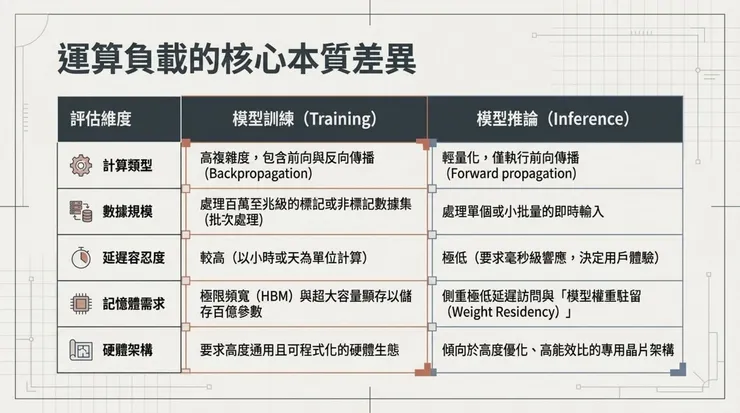

運算負載的核心特徵對比

為了理解硬體進程的變化,必須首先解析訓練與推論在計算邏輯上的本質差異。下表概述了兩者在計算、記憶體與通訊需求上的對比:

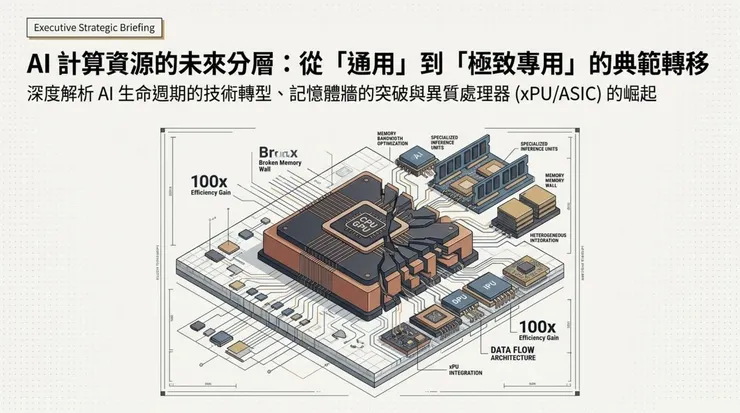

處理器架構的技術演進:從通用到極致專用

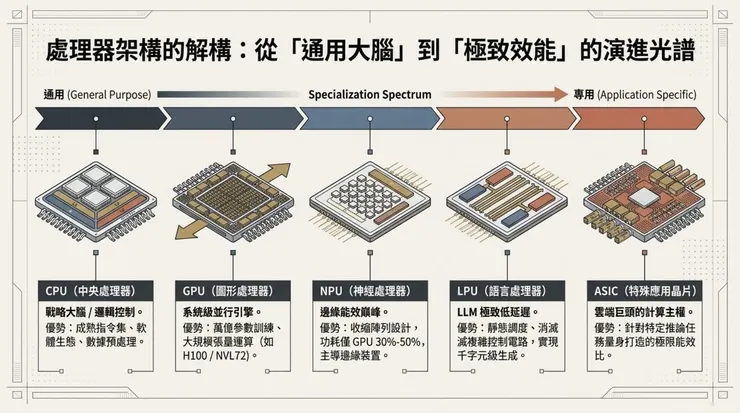

在 AI 計算的歷史進程中,處理器架構經歷了從中央處理器(CPU)的通用調度,到 GPU 的大規模並行,再到 NPU、LPU 與 ASIC 追求極致能效比的過程。

中央處理器(CPU)的協調與輕量化推論角色

儘管在處理大規模矩陣運算時效率不如加速器,但 CPU 始終是系統中的「戰略大腦」。其複雜的分支預測、亂序執行機制與成熟的指令集(如 x86 與 ARM),使其在處理順序邏輯、數據預處理與系統管理任務中具有不可替代的地位。在推論場景中,對於參數規模較小或對延遲要求不敏感的批處理任務,CPU 憑藉其極高的軟體生態相容性與大容量系統記憶體支持,依然是許多企業的首選。

圖形處理器(GPU)的並行革命與系統級進化

GPU 的出現徹底改變了深度學習的發展軌跡。其數千個小型核心能夠同時執行大規模的向量與矩陣運算,完美契合了神經網路訓練的需求 。NVIDIA 的 A100 與 H100 透過引入張量核心(Tensor Cores),進一步提升了混合精度運算的效率。然而,隨著模型規模邁向「萬億參數」時代,單一 GPU 已難以負擔,這推動了 GPU 向系統級架構(如 NVIDIA NVL72)演進,將整機架視為單一計算單元,透過高速互連技術實現內存共享與計算協同。

神經處理器(NPU)的能效巔峰與邊緣崛起

NPU 是針對人工神經網路運算高度優化的專用處理器。與 GPU 不同,NPU 捨棄了圖形渲染等無關功能,將大比例的晶片面積分配給收縮陣列(Systolic Array)與張量引擎,實現了卓越的「每瓦效能」(Performance per Watt)。在 AI PC 與行動裝置中,NPU 能在幾瓦的功耗下執行臉部識別、背景虛化與語音識別,釋放 CPU 與 GPU 以執行其他任務 。研究數據顯示,NPU 在執行特定推論任務時,其功耗僅為 GPU 的 30% 至 50% 。

語言處理器(LPU)與 Transformer 架構的極致匹配

Groq 提出的 LPU 代表了針對 LLM 推論的最新硬體前沿。LPU 採用的張量串流處理器(TSP)架構,徹底顛覆了傳統硬體的動態調度邏輯,改用編譯器導向的靜態調度。這種架構消除了硬體預算中的複雜控制電路,改由編譯器精確控制數據在晶片上的移動時間與空間路徑,從而實現了無與倫比的確定性延遲(Deterministic Latency)。LPU 在處理 LLM 的 Token 生成時,速度可達每秒數百至上千個 Token,遠超傳統 GPU。

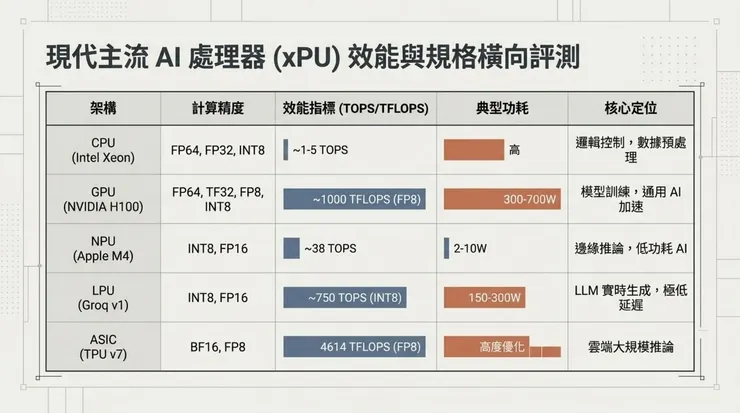

處理器架構效能指標橫向評測

下表展示了現代主流 AI 處理器在不同維度下的效能表現:

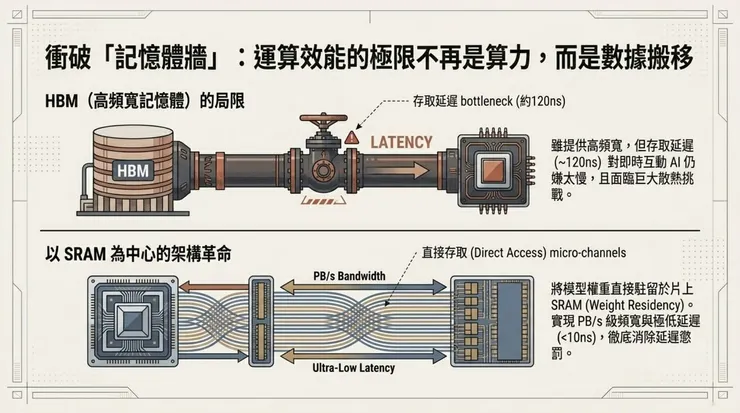

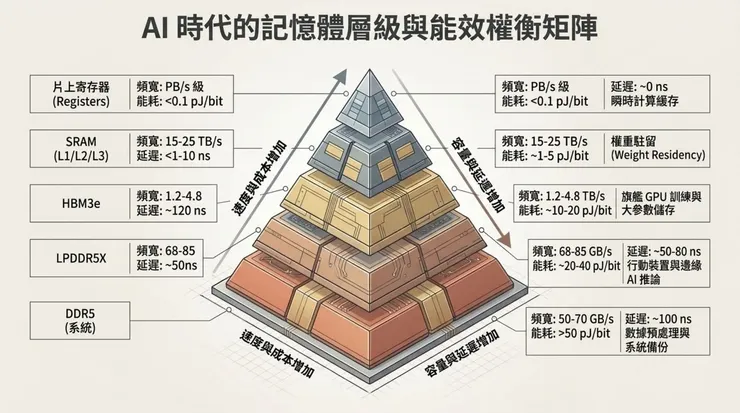

記憶體技術的進程與「記憶體牆」的突破

AI 硬體的效能瓶頸已從運算能力轉向數據移動效率,即所謂的「記憶體牆」(Memory Wall)。隨著模型參數規模的指數級增長,記憶體頻寬與延遲成為決定推論速度的核心因素。

高頻寬記憶體(HBM)的演進與局限

HBM 通過 3D 堆疊 DRAM 晶片並透過矽穿孔(TSV)與計算單元連接,提供了高達數 TB/s 的頻寬。HBM3e 目前已成為頂級 GPU 的標準配備。然而,HBM 面臨著製造成本昂貴、良率挑戰以及顯著的散熱難題。此外,雖然 HBM 提供高頻寬,但其存取延遲(約 100-120 ns)對於需要極速響應的自回歸(Autoregressive)解碼任務而言仍顯不足。

以 SRAM 為中心的架構變革

為了消除 HBM 的延遲懲罰,諸如 Groq LPU 與 Cerebras WSE 等架構選擇將模型權重直接駐留在片上靜態隨機存取記憶體(SRAM)中。SRAM 的頻寬可達 PB/s 級別,且存取延遲比 HBM 低一個數量級。這種設計雖然犧牲了單晶片的模型承載容量,但透過橫向擴展多個處理器(Scale-out),能實現毫秒級的生成速度,這對於互動式 AI(如即時語音助手)至關重要。

邊緣端記憶體與能效平衡

在行動裝置與物聯網節點中,低功耗雙倍數據速率記憶體(LPDDR)是主流選擇。LPDDR5X 等技術在提供接近 70-80 GB/s 頻寬的同時,保持了極低的待機功耗。隨著 4-bit 甚至 1-bit 量化技術的成熟,在受限記憶體空間內運行數十億參數的模型已成為可能。

記憶體層級能耗與延遲數據分析

下表詳細對比了 AI 系統中不同層級記憶體的技術規格:

電力需求與能源效率的生命週期轉移

AI 系統的電力消耗正成為全球能源結構中不容忽視的變量。從訓練到推論,電力需求的特徵發生了從「高密度衝擊」到「長尾持續消耗」的轉變 5。

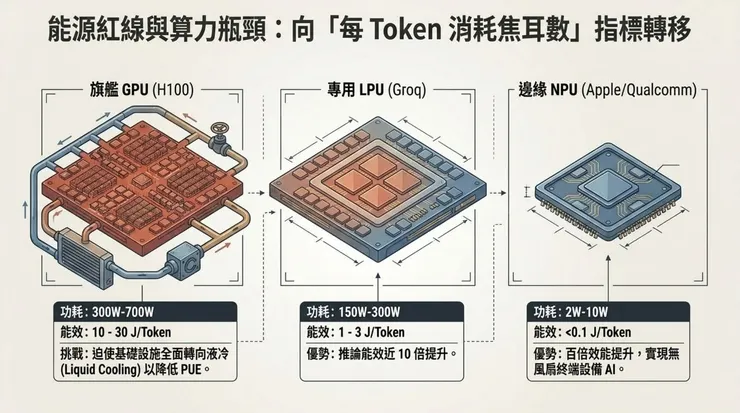

訓練階段的電力密集與冷卻技術

訓練大型模型(如 GPT-4)需要萬塊 GPU 連續運行數月,其電力需求以兆瓦(MW)計。這不僅涉及晶片的功耗,還包含龐大的冷卻系統能耗。研究指出,為了應對 H100 等晶片高達 700W 的熱設計功耗(TDP),數據中心正加速從氣冷向液冷轉型,以降低能源使用效率(PUE)值。

推論階段的能耗支配地位

雖然單次推論的能耗相對較小,但隨著應用普及,推論的累積能耗正成為 AI 環境足跡的主體。根據 Amazon 與 Google 的數據,推論任務已佔據 AI 總能耗的 60% 至 90% 5。一次典型的 LLM 查詢(如 ChatGPT)消耗約 2.9 Wh,幾乎是傳統網頁搜尋的 10 倍 46。這迫使開發者轉向更高效的硬體(如 NPU)與架構(如混合專家模型 MoE),以降低每生成一個 Token 的焦耳數。

能源消耗模型與優化數據

在評估推論能效時,業界常用「每 Token 消耗焦耳數」作為指標。下表對比了不同處理器在推論任務中的電力效率:

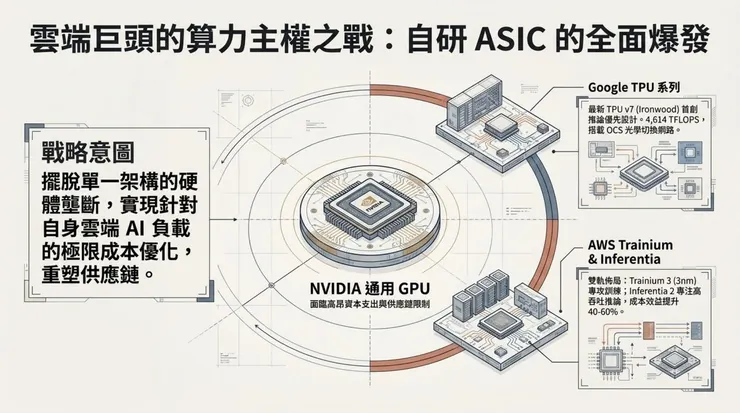

ASIC 的崛起:雲端巨頭的自研晶片戰略

面對 NVIDIA GPU 的高昂成本與供應限制,全球超大規模雲端供應商(Hyperscalers)正全面推進自研 ASIC 計劃,以實現計算主權與成本優化。

Google TPU:從 v1 到 v7 的技術跨越

Google 的 TPU 系列是 ASIC 成功的典範。TPU v4 引入了光學切換網路(OCS),顯著提升了跨機架的互連效率 。最新的 TPU v7 (Ironwood) 是首款完全針對「推論優先」設計的 TPU,旨在解決兆級參數模型的實時生成需求。Ironwood 在 FP8 精度下的計算力達到 4,614 TFLOPS,並配備了 192 GB 的超大 HBM 記憶體。

AWS Trainium 與 Inferentia 的協同佈局

Amazon 的策略是為訓練與推論量身定制兩套晶片。Trainium 3 採用 3nm 工藝,其計算效能較前代提升 4.4 倍,專為對標 NVIDIA 最新 GPU 而設計。而 Inferentia 2 則專注於高吞吐、低延遲的推論,其成本效益比傳統 GPU 高出 40% 至 60%。

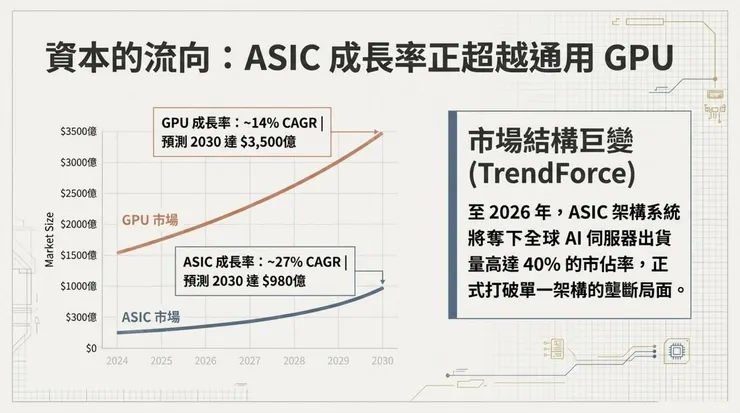

自研 ASIC 市場佔有率與發展趨勢

根據 Bloomberg 與 TrendForce 的市場分析數據,ASIC 的增長速度已超過 GPU:

網路連網與數據中心基礎設施的進程

AI 計算的效能極限不僅取決於單晶片,更受限於機架間與伺服器間的聯網效率。訓練與推論對網路架構的需求正在發生顯著分化。

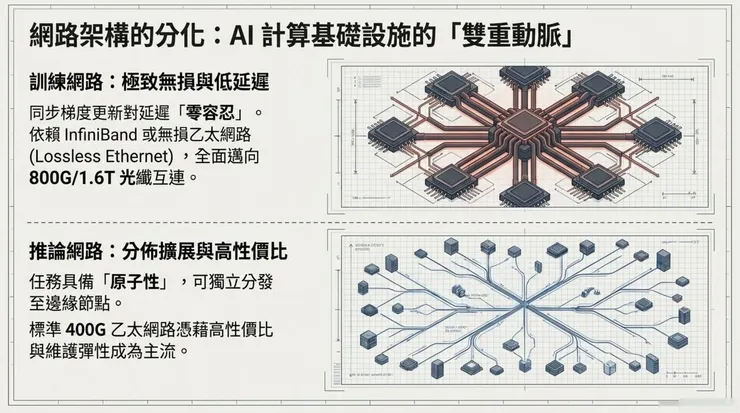

訓練網路:對低延遲與無損傳輸的極致追求

由於訓練過程涉及數千個 GPU 的同步梯度更新,任何網路延遲都會導致顯著的計算資源閒置。這使得 InfiniBand 與支援 RoCEv2 的無損乙太網路(Lossless Ethernet)成為標準 3。為了支持下個世代的訓練需求,800G 甚至 1.6T 的光纖互連技術已開始進入部署階段。

推論網路:地理分佈與彈性擴展

推論任務具有更強的「原子性」,這意味著每個請求可以獨立分發到不同的節點處理。因此,推論架構正從中心化的超級集群向地理分佈的邊緣節點延伸。在推論環境中,標準的 400G 乙太網路憑藉其極高的性價比與維護便利性,正逐漸取代昂貴的專用網絡技術。

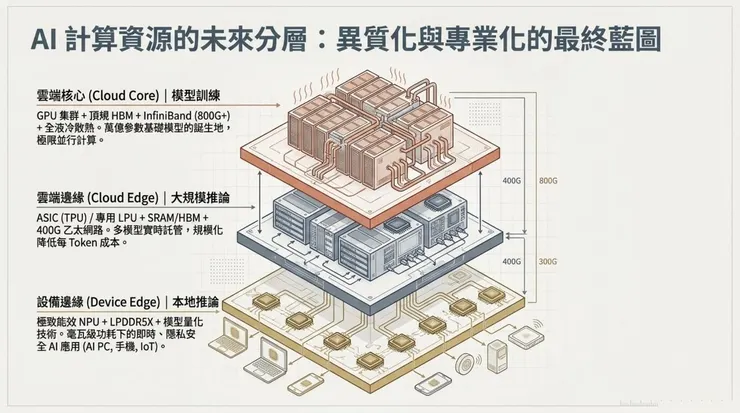

結論:AI 計算資源的未來分層

AI 硬體的發展進程清晰地指向了一個異質化與專業化的未來。訓練階段將繼續追求極限的並行能力與互連頻寬,由 GPU 與高端 ASIC(如 TPU, Trainium)主導。推論階段則將分裂為兩個路徑:雲端推論將側重於吞吐量與多模型託管能力,透過 ASIC 與高性能 LPU 實現規模化成本降低;而邊緣推論則將極致追求功耗比,透過 NPU 與專用微控制器(TinyML)實現 AI 隨處不在。

記憶體技術的創新(如 HBM4、3D-Stacked SRAM 與存內計算)將是打破「記憶體牆」的關鍵。同時,隨著電力與冷卻基礎設施成為 AI 擴展的硬性約束,軟硬體協同優化(量化、剪枝、MoE)將不再是選項,而是確保 AI 服務可持續運營的必然路徑。這場運算範式的變革,正引領人類進入一個從晶片設計到數據中心佈建全方位重構的新時代。